4.6 USB 3.0 Host Connector (J602)

The Mercury+ ST1 base board is equipped with a type-A USB 3.0 host connector.

If the mounted Mercury module features a USB controller, the module’s USB signals can be connected to

J602 via a multiplexer. Details on USB connections on the board are available in Section 6.5.

The power and data signals on this connector are ESD-protected.

4.7 USB 3.0 Device Connector (J600)

The Mercury+ ST1 base board is equipped with a type-B USB 3.0 device connector.

If the mounted Mercury module features a USB controller, the module’s USB signals can be connected to

J600 via a multiplexer. Details on USB connections on the board are available in Section 6.5.

The power and data signals on this connector are ESD-protected.

4.8 Micro USB 2.0 Device Connector (J601)

The micro USB connector on the board is connected to the FTDI device. It can be used for UART, SPI and

I2C communication. Refer to Section 6.5.2 for details on the FTDI device.

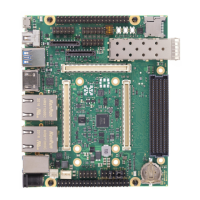

4.9 Gigabit Ethernet Ports (J1101/J1102)

The Mercury+ ST1 base board is equipped with two 10/100/1000 Mbit Ethernet ports. The capability of the

Ethernet interface depends on the connected Mercury module.

The RJ45 connectors are connected through magnetics directly to the Mercury module connector. For

details on the Ethernet interface, refer to Section 6.4.

4.10 SFP+ Connector (J1100)

The Mercury+ ST1 base board is equipped with a SFP+ socket. The capability of the SFP+ interface depends

on the connected Mercury module as well as on the plugged SFP+ module.

The SFP+ connector J1100 is connected by default to the Mercury module connector C, pins C-63/65 (TX

side) and C-66/68 (RX side).

4.11 MIPI Connectors (J1000/J1001)

The Mercury+ ST1 base board is equipped with two MIPI connectors, each with 2 signal lanes. The signals

available on these connectors are routed to/from the FPGA banks on the SoC/FPGA device on the Mercury

module. Refer to section 6.9 for details on connectivity options.

The pinout on the J1000 and J1001 connectors corresponds to the Raspberry Pi pinout. In order to receive

and transmit video signals through the links, FPGA support is required (video protocol implementation).

The signals on the connectors are ESD-protected.

D-0000-456-001 20 / 48 Version 02, 23.07.2020

Loading...

Loading...