Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved.

FIBOCOM L860-GL Series Hardware Guide Page 31 of 60

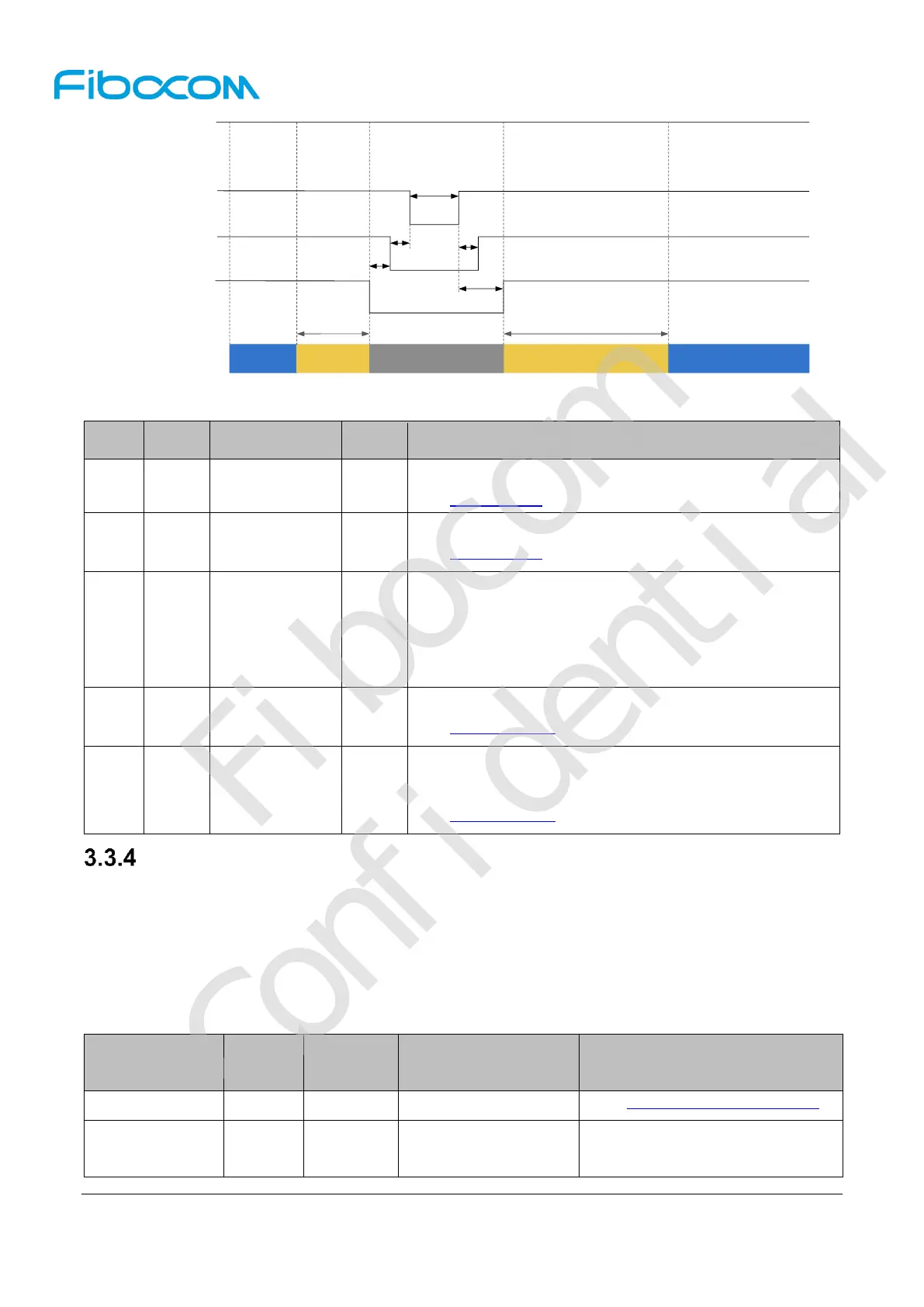

+3.3V

PERST#

RESET#

Module State

InitializationActivation

FCPO#

typical 15s

Activation

toff

Finalization OFF

AT+CFUN=0

toff2

toff1

ton1

ton2

tsd

Figure 3-9 Reset control timing2

nd

RESET# should be asserted after PERST#,

refer section 3.3.2

FCPO# should be asserted after RESET#,

refer section 3.3.2

Time to allow the WWAN module to fully discharge any

residual voltages before the pin could be de-asserted

again. This is required for both Pre-OS as well as Runtime

flow

RESET# should be de-asserted after FCPO#,

refer section 3.3.1.2

The time delay of PERST# de-asserted after FCPO#,

PERST# must always be the last to get de-asserted.

refer section 3.3.1.2

PCIe Link State

Modem has the lowest power consumption in D0 L1.2 PCIe link state. D3

cold

L2 will increase extra about

0.5mA power consumption. CLKREQ# can assert or de-assert in D3

cold

L2, but CLKREQ# shouldn’t be

changed again during D3

cold

L2. When CLKREQ# asserts in D3

cold

L2, it will increase extra 0.3mA power

consumption compared with CLKREQ# de-asserted in D3

cold

L2. We recommend keep CLKREQ# de-

asserted in D3

cold

L2.

Refer 3.2.3 Power Consumption

The extra 0.5mA is consumed on

PERST# pull down

Loading...

Loading...