Rev. 1.50 12 August 28, 2017 Rev. 1.50 13 August 28, 2017

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

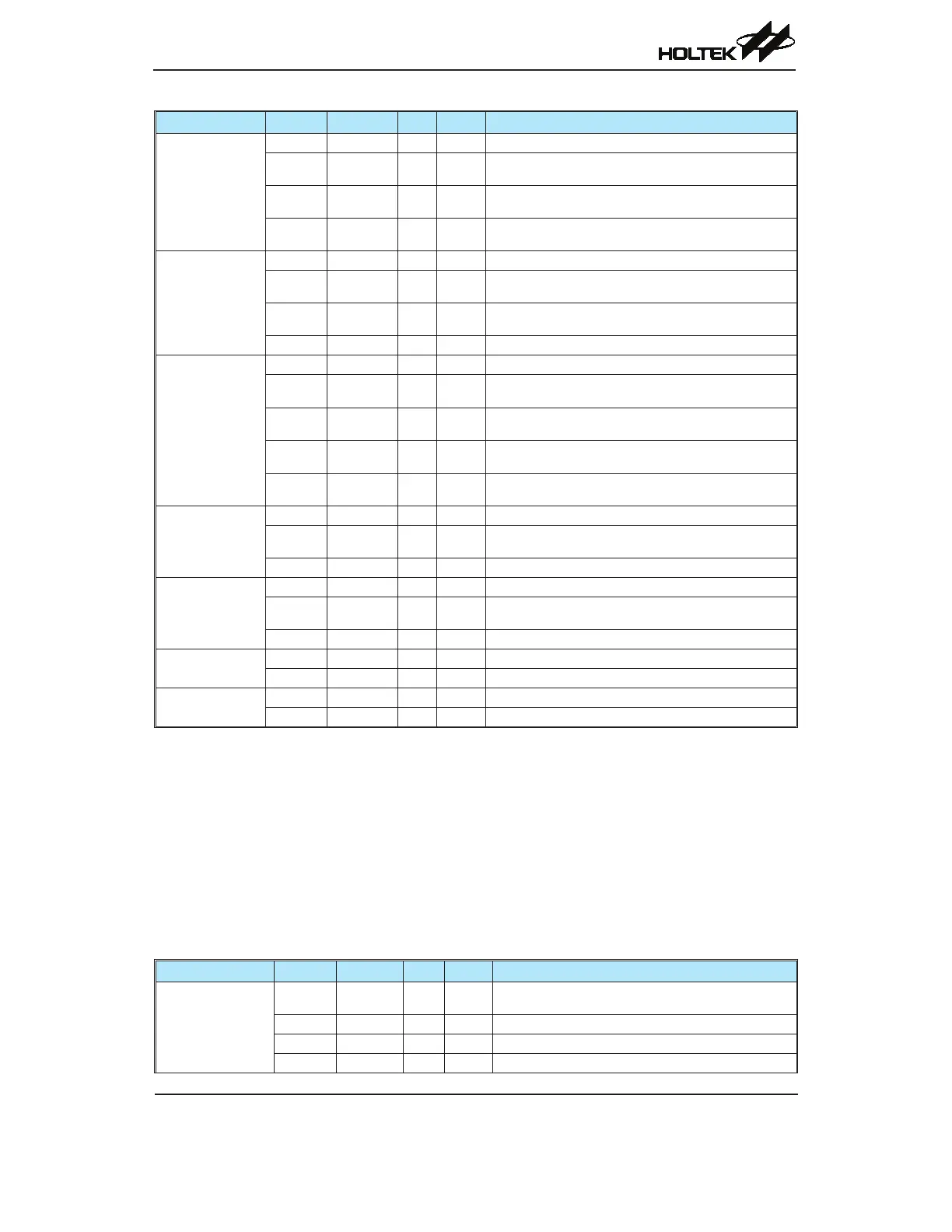

Pad Name Function OPT I/T O/T Description

PC2/SDO/SSEG0/

SCOM0

PC2 PCPU ST CMOS General purpose I/O. Register enabled pull-up.

SDO

SIMC0

IFS

— CMOS SPI data output

SSEG0

SLCDC0

SLCDC1

— SSEG Software controlled LCD segment output

SCOM0

SLCDC0

SLCDC1

— SCOM Software controlled LCD common output

PC3/SDI/SDA/

SSEG19

PC3 PCPU ST CMOS General purpose I/O. Register enabled pull-up.

SDI

SIMC0

IFS

ST — SPI data input

SDA

SIMC0

IFS

ST NMOS I

2

C data line

SSEG19 SLCDC3 — SSEG Software controlled LCD segment output

PC4/SCK/SCL/

SSEG1/SCOM1

PC4 PCPU ST CMOS General purpose I/O. Register enabled pull-up.

SCK

SIMC0

IFS

ST CMOS SPI serial clock

SCL

SIMC0

IFS

ST NMOS I

2

C clock line

SSEG1

SLCDC0

SLCDC1

— SSEG Software controlled LCD segment output

SCOM1

SLCDC0

SLCDC1

— SCOM Software controlled LCD common output

PC5/[INT1]/

SSEG11

PC5 PCPU ST CMOS General purpose I/O. Register enabled pull-up.

[INT1]

INTEG

IFS

ST — External Interrupt 1

SSEG11 SLCDC2 — SSEG Software controlled LCD segment output

PC6/[INT0]/

SSEG12

PC6 PCPU ST CMOS General purpose I/O. Register enabled pull-up.

[INT0]

INTEG

IFS

ST — External Interrupt 0

SSEG12 SLCDC2 — SSEG Software controlled LCD segment output

VDD&AVDD

VDD — PWR — Positive power supply

AVDD — PWR — A/D converter positive power supply

VSS&AVSS

VSS — PWR — Negative power supply, ground.

AVSS — PWR — A/D converter negative power supply, ground.

Note:I/T:Inputtype; O/T:Outputtype;

OPT:Optionalbycongurationoption(CO)orregisteroption;

CO:Congurationoption; ST:SchmittTriggerinput; AN:Analoginput;

CMOS:CMOSoutput; NMOS:NMOSoutput; AO:Analogoutput;

SSEG:SoftwarecontrolledLCDSEG; SCOM:SoftwarecontrolledLCDCOM;

HXT:Highfrequencycrystaloscillator; LXT:Lowfrequencycrystaloscillator

PWR:Power

*TheAVDDpinisinternallybondedtogetherwiththeVDDpinwhiletheAVSSpinisinternallybonded

togetherwiththeVSSpin.

AsthePinDescriptionSummarytableappliestothepackagetypewiththemostpins,notalloftheabovelisted

pinsmaybepresentonpackagetypeswithsmallernumbersofpins.

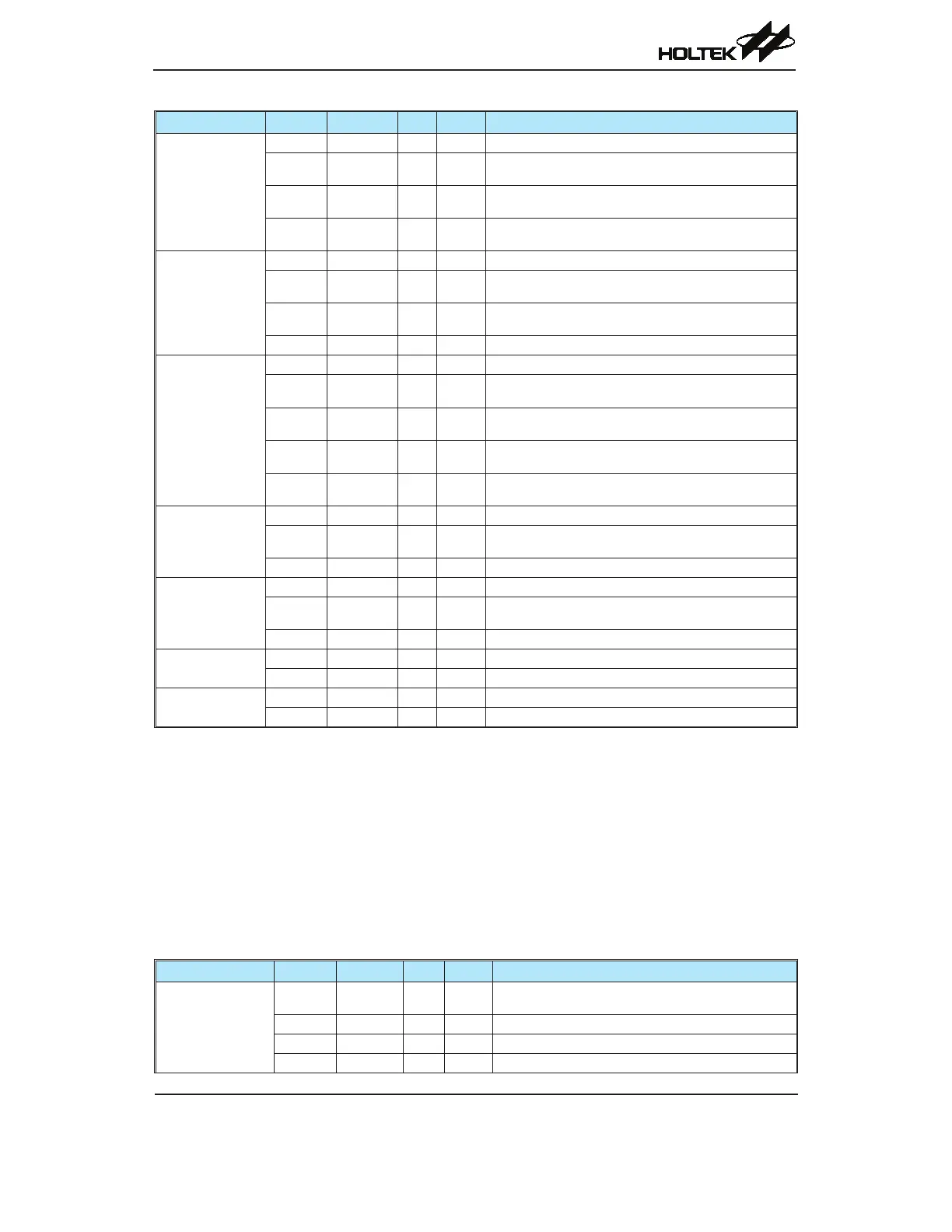

HT66F0185

Pad Name Function OPT I/T O/T Description

PA0/TP0/ICPDA/

OCDSDA

PA0

PAWU

PAPU

ST CMOS

General purpose I/O. Register enabled pull-up and

wake-up.

TP0 TMPC ST CMOS TM0 input/output

ICPDA — ST CMOS ICP Data/Address pin

OCDSDA — ST CMOS OCDS Data/Address pin, for EV chip only.

Loading...

Loading...