Rev. 1.50 160 August 28, 2017 Rev. 1.50 161 August 28, 2017

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

Bit2 TXBRK:Transmitbreakcharacter

0:Nobreakcharacteristransmitted

1:Breakcharacterstransmit

TheTXBRKbitistheTransmitBreakCharacterbit.Whenthisbitisequalto“0”,

therearenobreakcharactersandtheTXpinoperatsnormally.Whenthebitisequalto

“1”,therearetransmitbreakcharactersandthetransmitterwillsendlogiczeros.When

thisbitisequalto“1”,afterthebuffereddatahasbeentransmitted,thetransmitter

outputisheldlowforaminimumofa13-bitlengthanduntiltheTXBRKbitisreset.

Bit1 RX8:Receivedatabit8for9-bitdatatransferformat(readonly)

Thisbitisonlyusedif9-bitdatatransfersareused,inwhichcasethisbitlocationwill

storethe9

th

bitofthereceiveddataknownasRX8.TheBNObitisusedtodetermine

whetherdatatransfesarein8-bitor9-bitformat.

Bit0 TX8:Transmitdatabit8for9-bitdatatransferformat(writeonly)

Thisbitisonlyusedif9-bitdatatransfersareused,inwhichcasethisbitlocation

willstorethe9

th

bitofthetransmitteddataknownasTX8.TheBNObitisusedto

determinewhetherdatatransfesarein8-bitor9-bitformat.

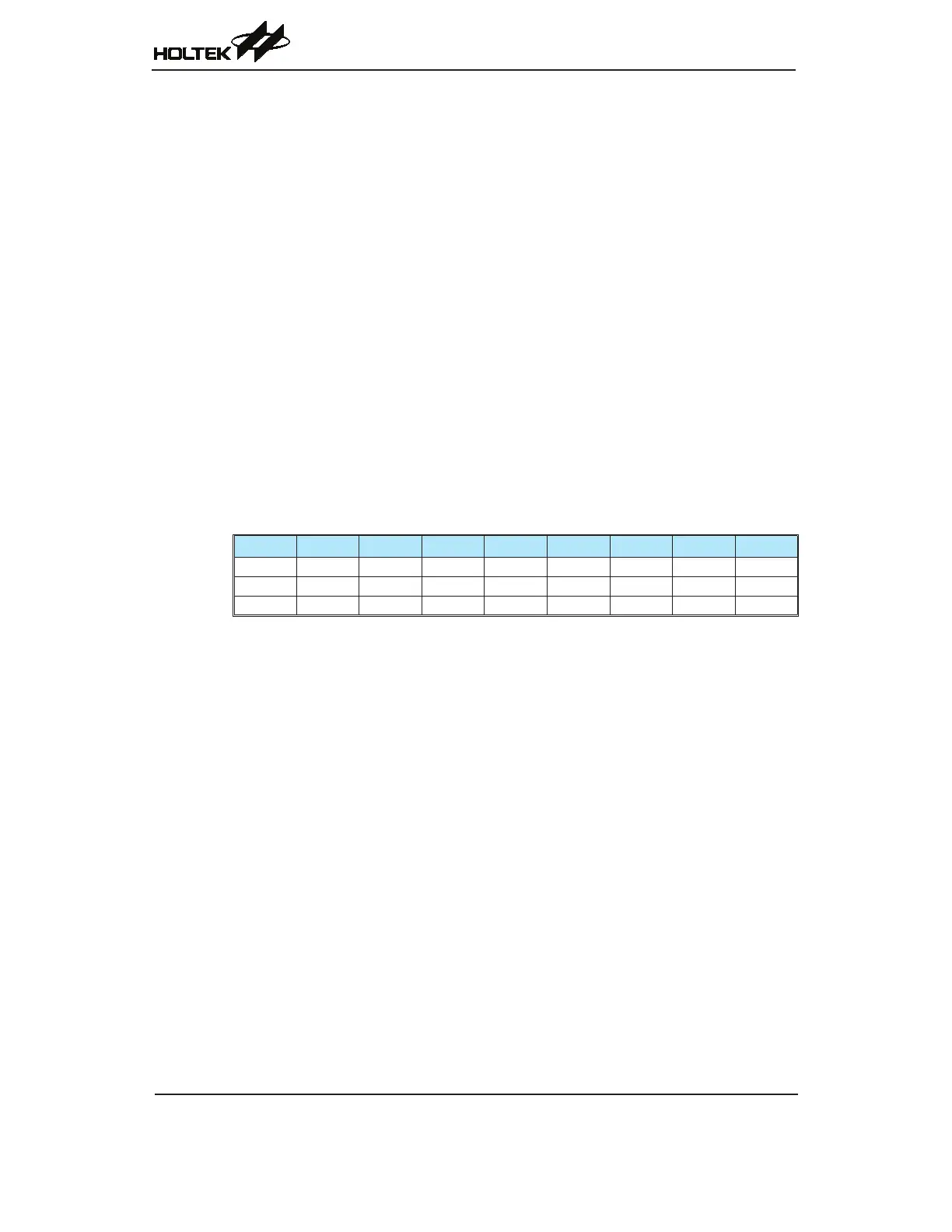

UCR2 Register

TheUCR2registeristhesecondoftheUARTcontrolregistersandservesseveralpurposes.One

ofitsmainfunctionsistocontrolthebasicenable/disableoperationiftheUARTTransmitterand

ReceiveraswellasenablingthevariousUARTinterruptsources.Theregisteralsoservestocontrol

thebaudratespeed,receiverwake-upfunctionenableandtheaddressdetectfunctionenable.

Furtherexplanationoneachofthebitsisgivenbelow.

Bit 7 6 5 4 3 2 1 0

Name TXEN RXEN BRGH ADDEN WAKE RIE TIIE TEIE

R/W R/W R/W R/W R/W R/W R/W R/W R/W

POR 0 0 0 0 0 0 0 0

Bit7 TXEN:UARTTransmitterenablecontrol

0:UARTTransmitterisdisabled

1:UARTTransmitterisenabled

TheTXENbitistheTransmitterEnableBit.Whenthisbitisequalto“0”,the

transmitterwillbedisabledwithanypendingdatatransmissionsbeingaborted.In

additionthebufferswillbereset.InthissituationtheTXpinwillbeotherpin-shared

functionalpin.IftheTXENbitisequalto“1”andtheUARTENbitisalsoequalto

1,thetransmitterwillbeenabledandtheTXpinwillbecontrolledbytheUART.

ClearingtheTXENbitduringatransmissionwillcausethedatatransmissiontobe

abortedandwillresetthetransmitter.Ifthissituationoccurs,theTXpinwillbeother

pin-sharedfunctionalpin.

Bit6 RXEN:UARTReceiverenablecontrol

0:UARTReceiverisdisabled

1:UARTReceiverisenabled

TheRXENbitistheReceiverEnableBit.Whenthisbitisequalto“0”,thereceiver

willbedisabledwithanypendingdatareceptionsbeingaborted.Inadditionthe

receiverbufferswillbereset.InthissituationtheRXpinwillbeotherpin-shared

functionalpin.IftheRXENbitisequalto“1”andtheUARTENbitisalsoequal

to1,thereceiverwillbeenabledandtheRXpinwillbecontrolledbytheUART.

ClearingtheRXENbitduringareceptionwillcausethedatareceptiontobeaborted

andwillresetthereceiver.Ifthissituationoccurs,theRXpinwillbeotherpin-shared

functionalpin.

Loading...

Loading...