Rev. 1.50 168 August 28, 2017 Rev. 1.50 169 August 28, 2017

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

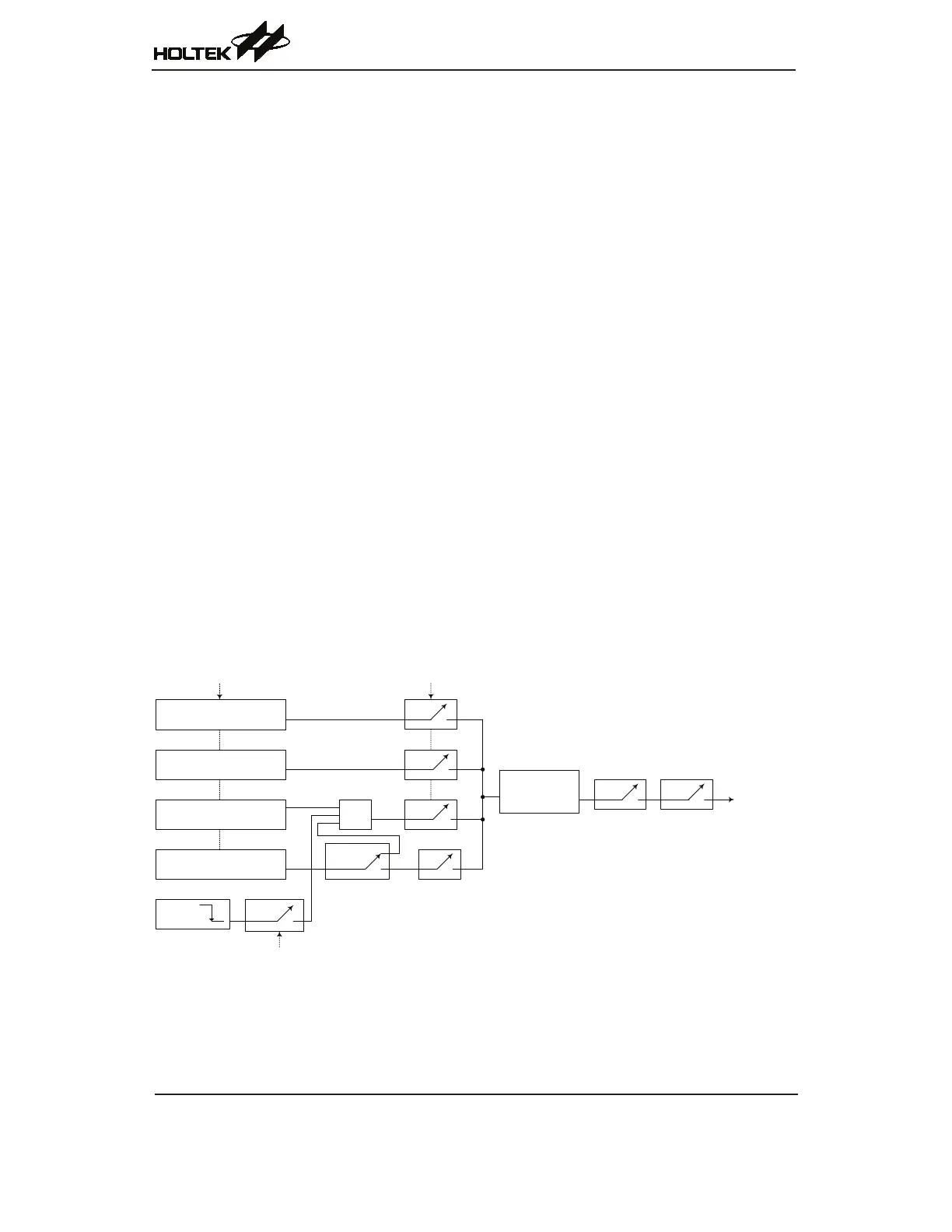

UART Interrupt Structure

SeveralindividualUARTconditionscangenerateaUARTinterrupt.Whentheseconditionsexist,

alowpulsewillbegeneratedtogettheattentionofthemicrocontroller.Theseconditionsarea

transmitterdataregisterempty,transmitteridle,receiverdataavailable,receiveroverrun,address

detectandanRXpinwake-up.Whenanyoftheseconditionsarecreated,ifitscorresponding

interruptcontrolisenabledandthestackisnotfull,theprogramwilljumptoitscorresponding

interruptvectorwhereitcanbeservicedbeforereturningtothemainprogram.Fourofthese

conditionshavethecorrespondingUSRregisteragswhichwillgenerateaUARTinterruptifits

associatedinterruptenablecontrolbitintheUCR2registerisset.Thetwotransmitterinterrupt

conditionshavetheirowncorrespondingenablecontrolbits,whilethetworeceiverinterrupt

conditionshaveasharedenablecontrolbit.Theseenablebitscanbeusedtomaskoutindividual

UARTinterruptsources.

Theaddressdetectcondition,whichisalsoaUARTinterruptsource,doesnothaveanassociated

flag,butwillgenerateaUARTinterruptwhenanaddressdetectconditionoccursifitsfunction

isenabledbysettingtheADDENbitintheUCR2register.AnRXpinwake-up,whichisalsoa

UARTinterruptsource,doesnothaveanassociatedag,butwillgenerateaUARTinterruptifthe

microcontrolleriswokenupfromIDLE0orSLEEPmodebyafallingedgeontheRXpin,ifthe

WAKEandRIEbitsintheUCR2registerareset.NotethatintheeventofanRXwake-upinterrupt

occurring,therewillbeacertainperiodofdelay,commonlyknownastheSystemStart-upTime,for

theoscillatortorestartandstabilizebeforethesystemresumesnormaloperation.

NotethattheUSRregisterflagsarereadonlyandcannotbeclearedorsetbytheapplication

program,neitherwilltheybeclearedwhentheprogramjumpstothecorrespondinginterrupt

servicingroutine,asisthecaseforsomeoftheotherinterrupts.Theflagswillbecleared

automaticallywhencertainactionsaretakenbytheUART,thedetailsofwhicharegiveninthe

UARTregistersection.TheoverallUARTinterruptcanbedisabledorenabledbytherelated

interruptenablecontrolbitsintheinterruptcontrolregistersofthemicrocontrollertodecidewhether

theinterruptrequestedbytheUARTmoduleismaskedoutorallowed.

USR Register

Transmitter Empty Flag TXIF

0

1

WAKE

Interrupt

signal to MCU

Transmitter Idle Flag TIDLE

Receiver Overrun Flag

OERR

Receiver Data Available

RXIF

RX Pin

Wake-up

UCR2 Register

OR

0

1

ADDEN

0

1

RIE

0

1

TIIE

0

1

TEIE

0

1

RX7 if BNO=0

RX8 if BNO=1

UCR2 Register

UART Interrupt

Request Flag

URF

0

1

URE

0

1

EMI

UART Interrupt Structure

Loading...

Loading...