2-20 Chapter2

HP ESA Status Registers

Using the Analyzer Status Registers

The Questionable Status condition register continuously monitors the

hardware and firmware status of the analyzer. Condition registers are

read-only. To query the condition register, send the command

:STATus:QUEStionable:CONDition? The response will be the decimal

sum of the bits which are set to 1. For example, if bit number 9 and bit

number 3 are set to 1, the decimal sum of the 2 bits is 512 plus 8. So the

decimal value 520 is returned.

The transition filter specifies which types of bit state changes in the

condition register will set corresponding bits in the event register. The

changes may be positive (from 0 to 1) or negative (from 1 to 0). Send the

command :STATus:QUEStionable:NTRansition <num> (negative

transition) or :STATus:QUEStionable:PTRansition <num> (positive

transition) where <num> is the sum of the decimal values of the bits you

want to enable.

The Questionable Status event register latches transition events from

the condition register as specified by the transition filters. Event

registers are destructive read-only. Reading data from an event register

will clear the content of that register. To query the event register, send

the command :STATus:QUEStionable[:EVENt]?

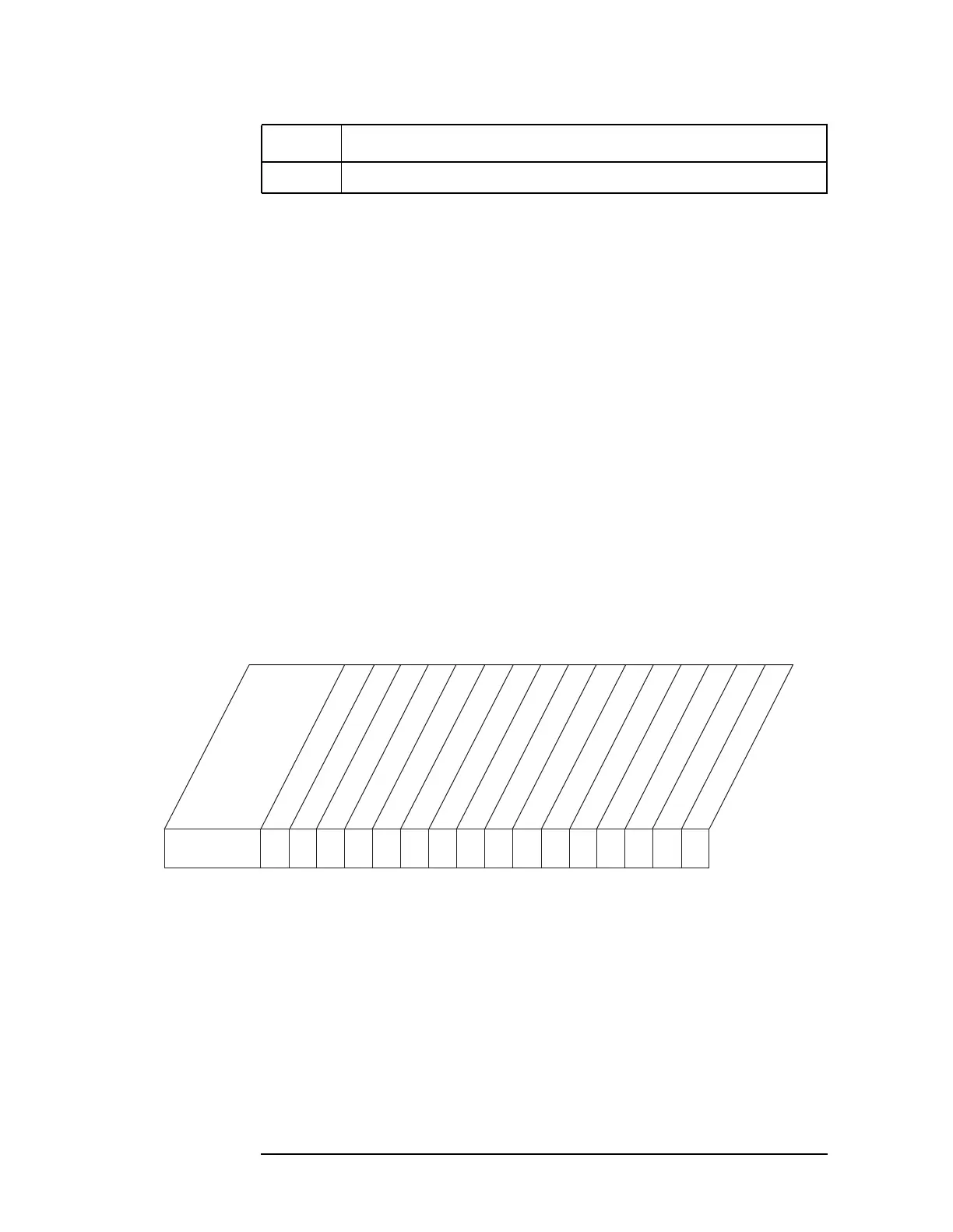

Figure 2-7.

The Questionable Status event enable register lets you choose which

bits in the Questionable Status Event Register will set the summary bit

(bit 3 of the Status Byte Register) to 1. Send the command

:STATus:QUEStionable:ENABle <num> where <num> is the sum of the

decimal values of the bits you want to enable. For example, to enable bit

9 and bit 3 so that whenever either of those bits is set to 1, the

Questionable Status Summary bit of the Status Byte Register will be

15 Always Zero (0).

Bit Description

Bit Number

7

89101112131415

6

5

432

1

0

2048

512

32

16

4

8

1

16384

8192

4096

1024

128

256

64

Decimal Value

32768

2

ck768a

Questionable Event Enable RegisterStatus

STATus:QUEStionable:ENABle <num>

STATus:QUEStionable:ENABle?

Loading...

Loading...