• False Start Bit Detection.

• Complete Status Reporting Capabilities.

• Line Break Generation and Detection.

• Internal Diagnostic Capabilities.

Loopback Controls for Communications Link Fault

Isolation.

Break, Parity, Overrun, Framing Error Simulation.

• Full Prioritized Interrupt System Controls.

All communications protocol

is

a function

of

the system microcode

and must be loaded before the adapter

is

operational. All pacing ofthe

interface and control signal status must be handled by the system

software.

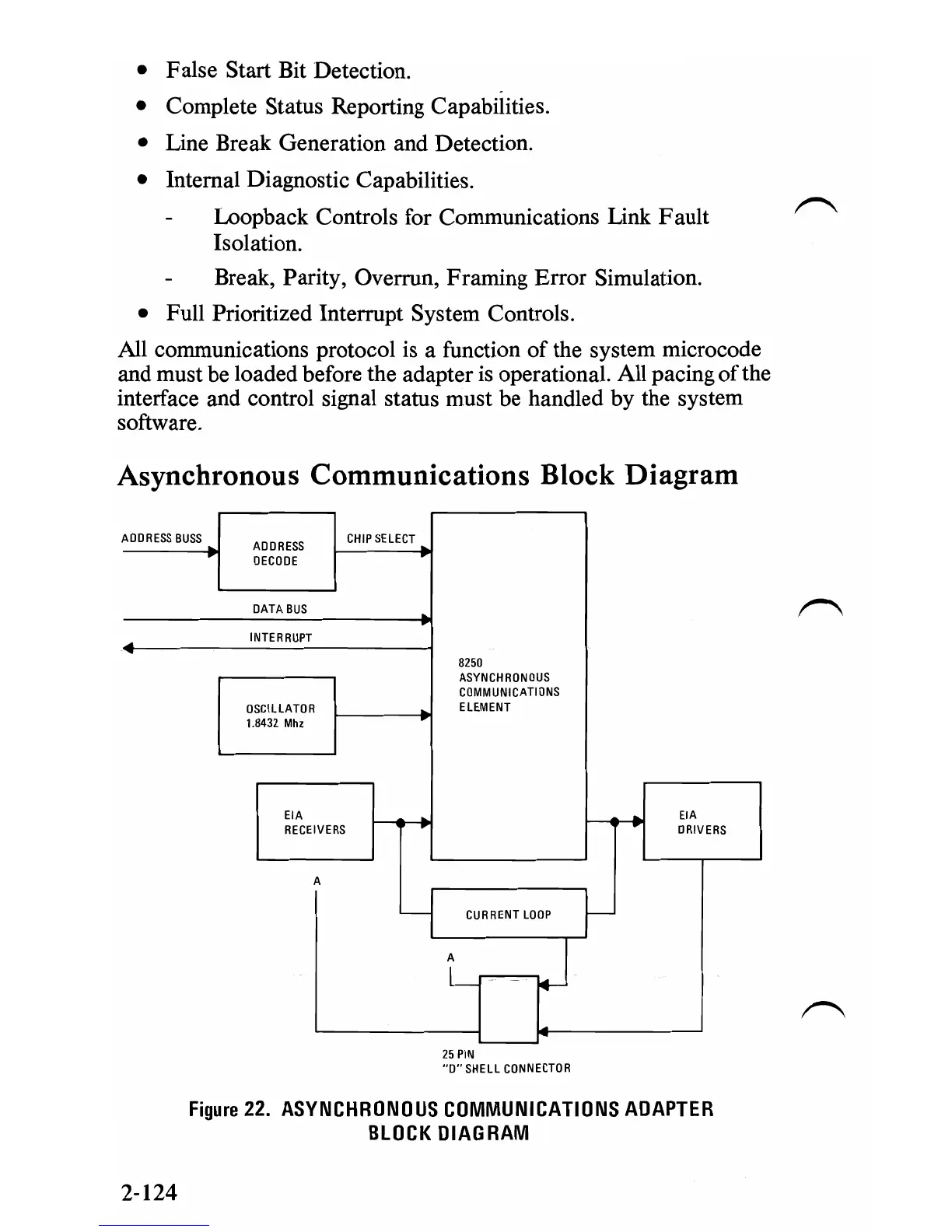

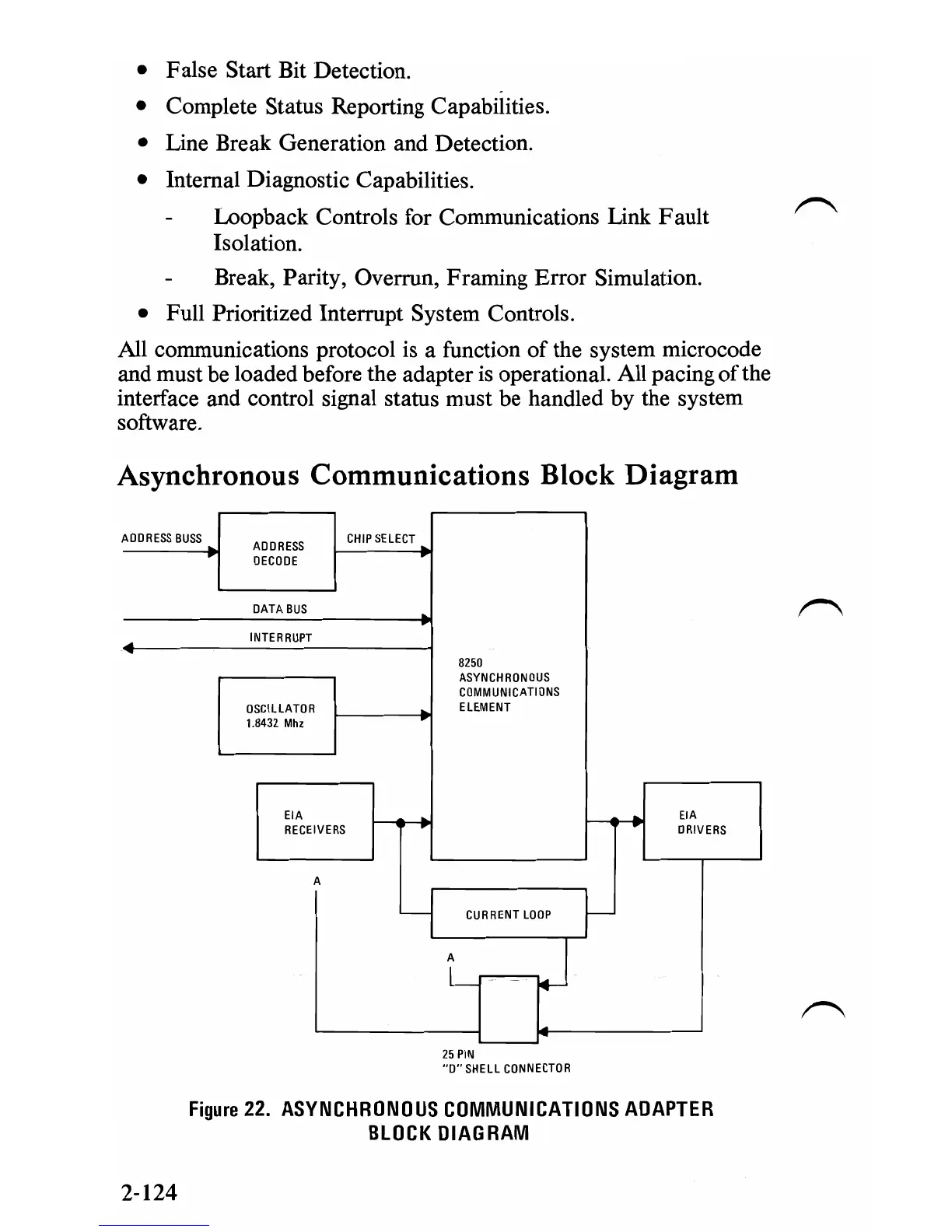

Asynchronous Communications Block Diagram

ADDRESS

BUSS

CHIP

SELECT

ADDRESS

DECODE

DATA

BUS

INTERRUPT

8250

ASYNCH

RONOUS

COMMUNICATIONS

OSCILLATOR

ELEMENT

--"

1.8432

Mhz

EIA

EIA

RECEIVERS

DRIVERS

A

CURRENT

LOOP

Y

~

A

L

J

L.

25

PIN

"D"SHELLCONNECTOR

Figure

22.

ASYNCHRONOUS

COMMUNICATIONS

ADAPTER

BLOCK

DIAGRAM

2-124

Loading...

Loading...