Interrupt Identification Register

The

INS8250

has an on-chip interrupt capability that allows for

complete flexibility in interfacing to all the popular microprocessors

presently available. In order to provide minimum software overhead

during data character transfers, the

INS8250

prioritizes interrupts into

r"\

four levels. The four levels

of

interrupt conditions are as follows:

Receiver Line Status (priority 1); Received

Data

Ready (priority 2);

Transmitter Holding Register Empty (priority 3); and

MODEM

Status (priority 4).

Information indicating that a prioritized interrupt

is

pending and the

type

of

that interrupt are stored in the Interrupt Identification Register

(refer to Table 5). The Interrupt Identification Register (IIR), when

addressed during chip-select time, freezes the highest priority interrupt

pending and no other interrupts are acknowledged until that particular

interrupt

is

serviced by the CPU. The contents

of

the

IIR

are indicated

and described below.

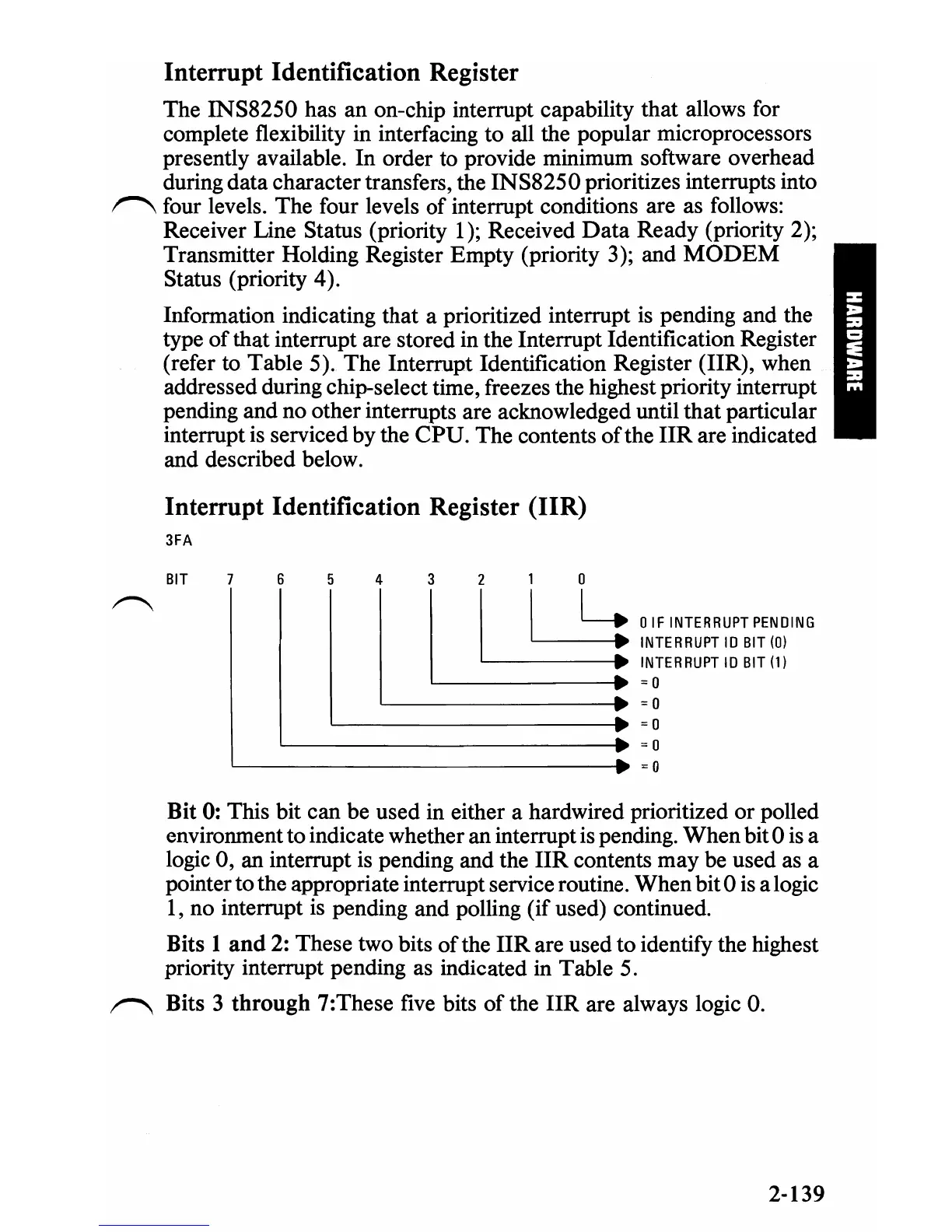

Interrupt Identification Register (IIR)

3FA

BIT

6

5 4 3 2 1 0

I

L:

0

If

INTERRUPTPENDING

I

I

~~

INTERRUPT

10

BIT

(0)

INTER

RUPT

10

BIT (1)

I

-

'--------~

~

0

'-----------

....

~

0

'-------------~

~O

L-

____________

~

~O

'-----------------

....

~O

Bit 0: This bit can be used in either a hardwired prioritized or polled

environment to indicate whether an interrupt is pending. When bit 0

is

a

logic 0, an interrupt is pending and the

IIR

contents may be used as a

pointer to the appropriate interrupt service routine. When bit 0

is

a logic

1,

no interrupt

is

pending and polling (if used) continued.

Bits 1

and

2: These two bits

ofthe

IIR

are used to identify the highest

priority interrupt pending as indicated in Table 5.

,.,-....,

Bits 3

through

7:These five bits

of

the

IIR

are always logic

O.

2-139

Loading...

Loading...