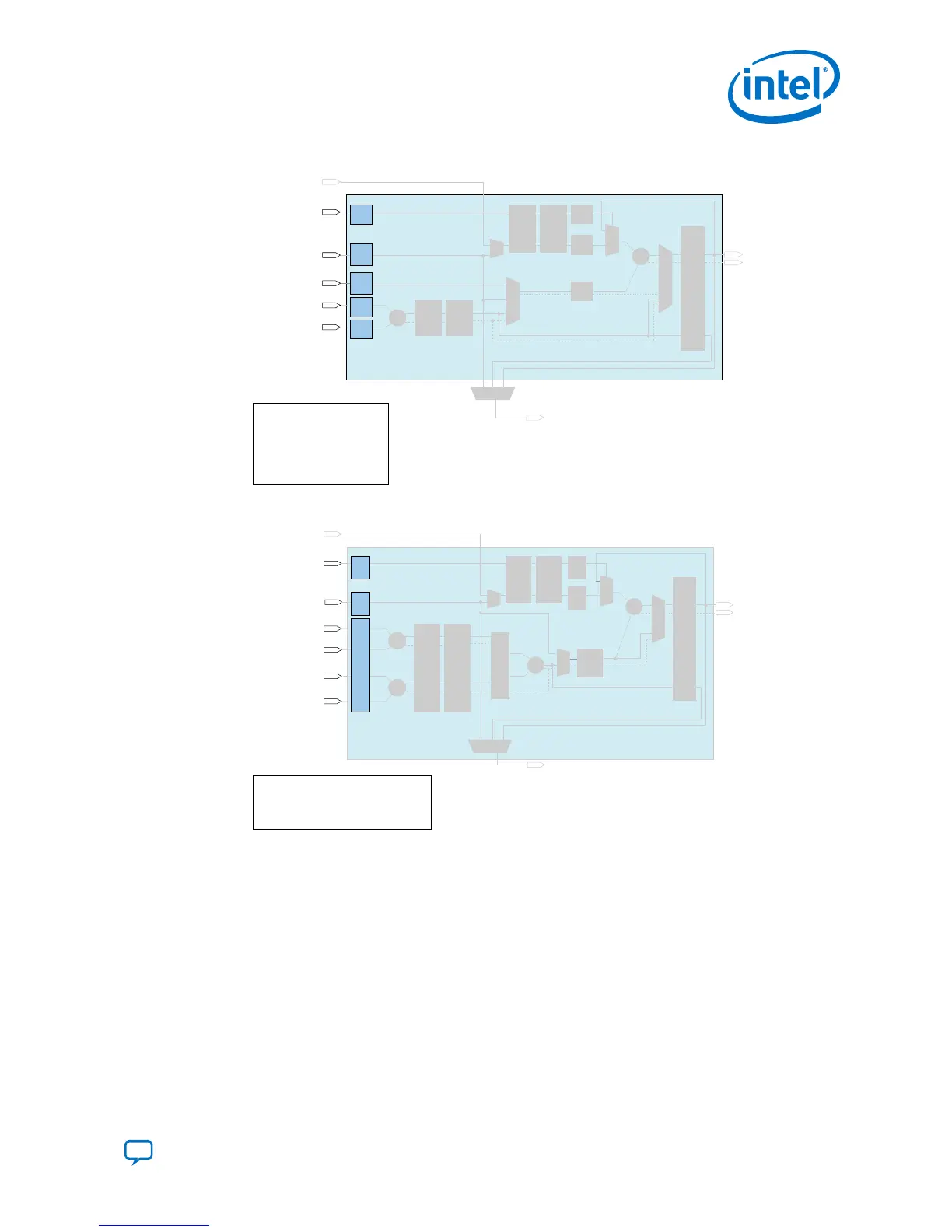

Figure 10. Location of Input Register for FP32 Operation Modes

fp32_chainout[31:0]

fp32_chainin[31:0]

accumulate

fp32_adder_a[31:0]

fp32_adder_b[31:0]

fp32_result[31:0]

Multiplier

Adder

*Pipeline

Register

*Pipeline

Register

*Pipeline

Register

fp32_mult_invalid

fp32_mult_inexact

fp32_mult_overflow

fp32_mult_underflow

fp32_adder_invalid

fp32_adder_inexact

fp32_adder_overflow

fp32_adder_underflow

*Pipeline

Register

Output

Register

Bank

fp32_mult_a[31:0]

fp32_mult_b[31:0]

1

2

3

4

5

1 - accumulate_clken

2 - fp32_adder_a_clken

3 - fp32_adder_b_clken

4 - fp32_mult_a_clken

5 - fp32_mult_b_clken

Legend:

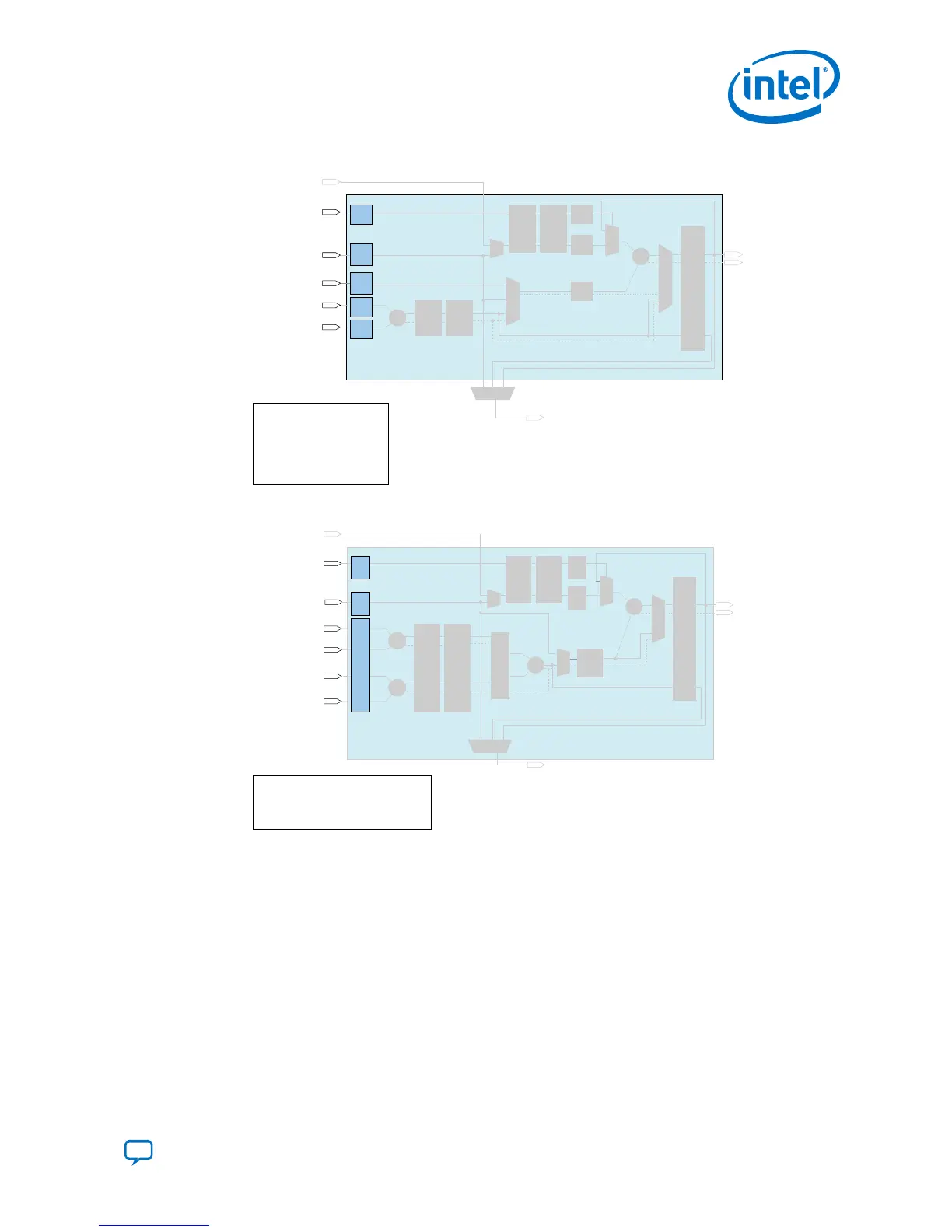

Figure 11. Location of Input Register for FP16 Operation Modes

fp32_chainout[31:0]

fp32_chainin[31:0]

accumulate

fp32_adder_a[31:0]

fp16_mult_top_a[15:0]

fp32_result[31:0]

Top

Multiplier

Adder

*Pipeline

Register

*Pipeline

Register

*Pipeline

Register

*Pipeline

Register

Output

Register

Bank

fp16_mult_top_b[15:0]

fp16_mult_bot_a[15:0]

Bottom

Multiplier

fp16_mult_bot_b[15:0]

Register

Register

Adder

1

2

3

Legend:

1 - accumulate_clken

2 - fp32_adder_a_clken

3 - fp16_mult_input_clken

fp16_mult_top_invalid

fp16_mult_top_underflow

fp16_mult_top_overflow

fp32_adder_invalid

fp32_adder_inexact

fp32_adder_overflow

fp32_adder_underflow

fp16_mult_top_inexact

fp16_mult_bot_invalid

fp16_mult_bot_underflow

fp16_mult_bot_overflow

fp16_mult_bot_inexact

fp16_adder_invalid

fp16_adder_inexact

fp16_adder_overflow

fp16_adder_underflow

fp16_mult_top_infinite

fp16_mult_top_zero

fp16_mult_bot_infinite

fp16_mult_top_zero

fp16_adder_zero

fp16_adder_infinite

All the registers in the DSP blocks are positive-edge triggered and cleared on power

up. Each multiplier operand can feed an input register or a multiplier directly,

bypassing the input registers.

The following variable precision DSP block signals control the input registers within the

variable precision DSP block:

•

CLK

•

ENA[2..0]

•

CLR[0]

2. Intel Agilex Variable Precision DSP Blocks Architecture

UG-20213 | 2019.04.02

Send Feedback

Intel

®

Agilex

™

Variable Precision DSP Blocks User Guide

21

Loading...

Loading...