3.1.2. 8 x 8 (unsigned) or 9 x 9 (signed) Sum of 4 Mode

The 8 x 8 (unsigned) or 9 x 9 sum of 4 mode uses the following equations:

resulta = (ax * ay)+(bx * by)+(cx * cy)+(dx * dy)

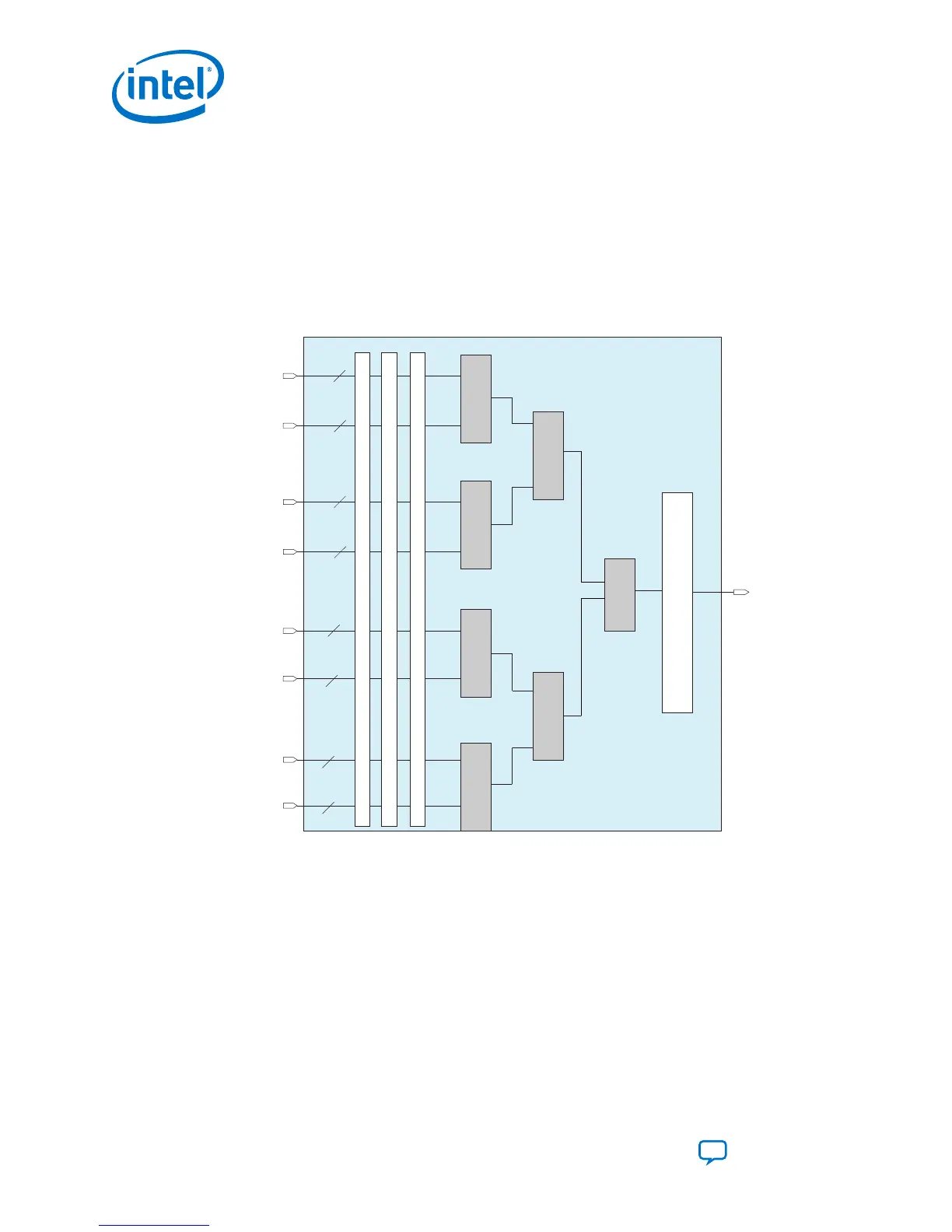

Figure 18. 9 × 9 Sum of 4

In this figure, the variables are defined as follows:

• n = 8 and m = 8 for 8 x 8 unsigned operands

• n = 9 and m = 9 for 9 x 9 signed operands

resulta[(63..0]

Multiplier

x

Multiplier

x

Input Register Bank

ay [(n-1)..0]

ax [(n-1)..0]

9

9

Variable-Precision DSP Block

by [(n-1)..0]

bx [(n-1)..0]

9

9

Output Register Bank

*1st Pipeline Register

*2nd Pipeline Register

*This block diagram shows the functional representation of the DSP block.

The pipeline registers are embedded within the various circuits of the DSP block.

x

x

Multiplier

Multiplier

+

+

+

cx [(n-1)..0]

cy [(n-1)..0]

dy [(n-1)..0]

dx [(n-1)..0]

9

9

9

9

Adder

Adder

Adder

3.1.3. Multiplier Adder Sum Mode

The multiplier adder sum mode uses the equations:

• resulta = (bx * by) + (ax * ay) to calculate the sum of the two 18 x 19

multiplications.

• resulta = (bx * by) - (ax * ay) to calculate the difference of the two 18 x 19

multiplications.

3. Intel Agilex Variable Precision DSP Blocks Operational Modes

UG-20213 | 2019.04.02

Intel

®

Agilex

™

Variable Precision DSP Blocks User Guide

Send Feedback

34

Loading...

Loading...