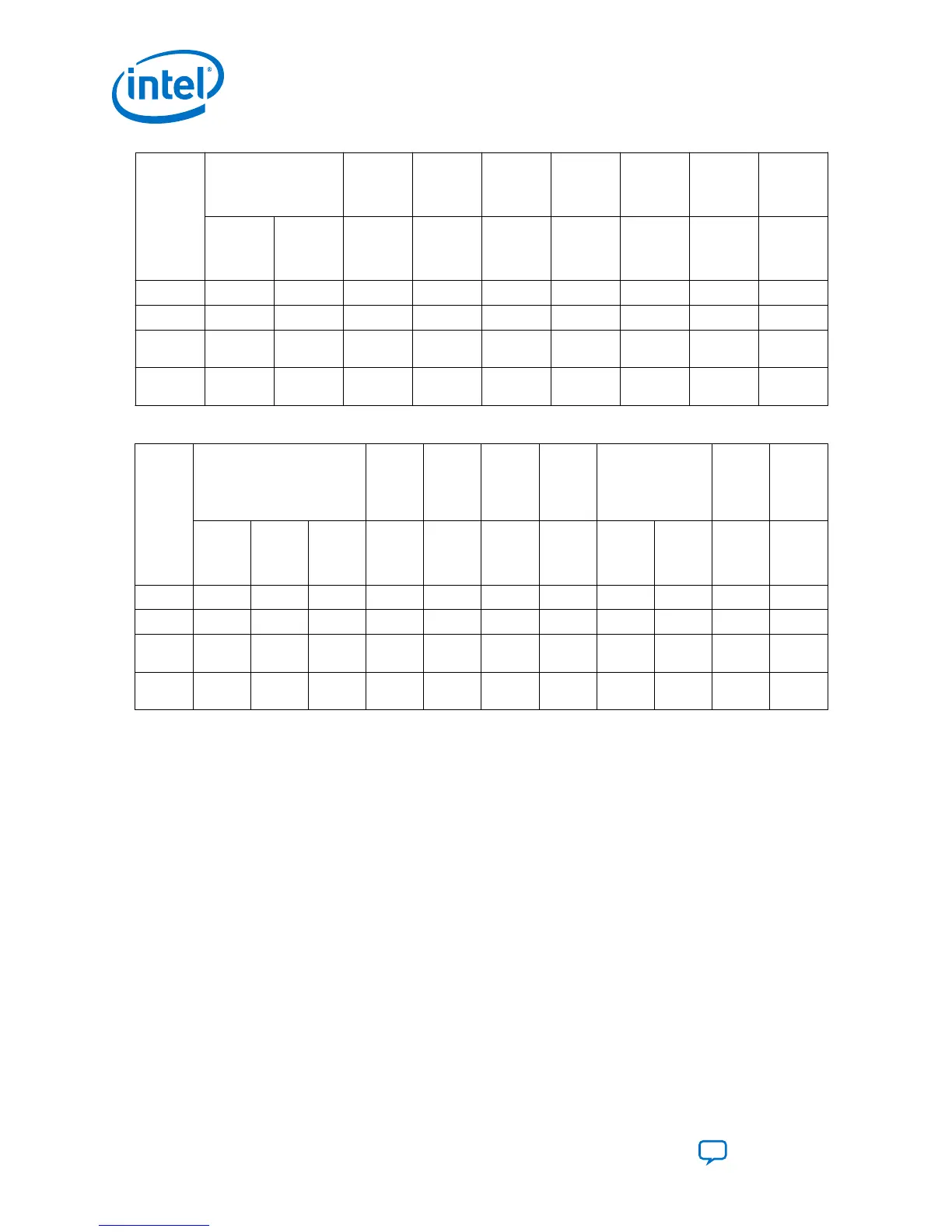

Latency Data Input Register Adder 1st

Pipeline

Register

Adder

2nd

Pipeline

Register

Multiplier

1st

Pipeline

Register

Multiplier

2nd

Pipeline

Register

Adder

Input

Register

Adder

Pipeline

Register

Output

Register

fp32_add

er_a_clke

n

fp16_mul

t_input_c

lken

fp32_add

er_a_chai

nin_pl_cl

ken

fp32_add

er_a_chai

nin_2nd_

pl_clken

mult_pipe

line_clke

n

mult_2nd

_pipeline

_clken

adder_inp

ut_clken

adder_pl_

clken

output_cl

ken

1 Disable Disable Disable Disable Disable Disable Disable Disable Enable

2 Enable Enable Disable Disable Disable Disable Disable Disable Enable

≥3 Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Enable Enable

≥4 Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Enable Enable

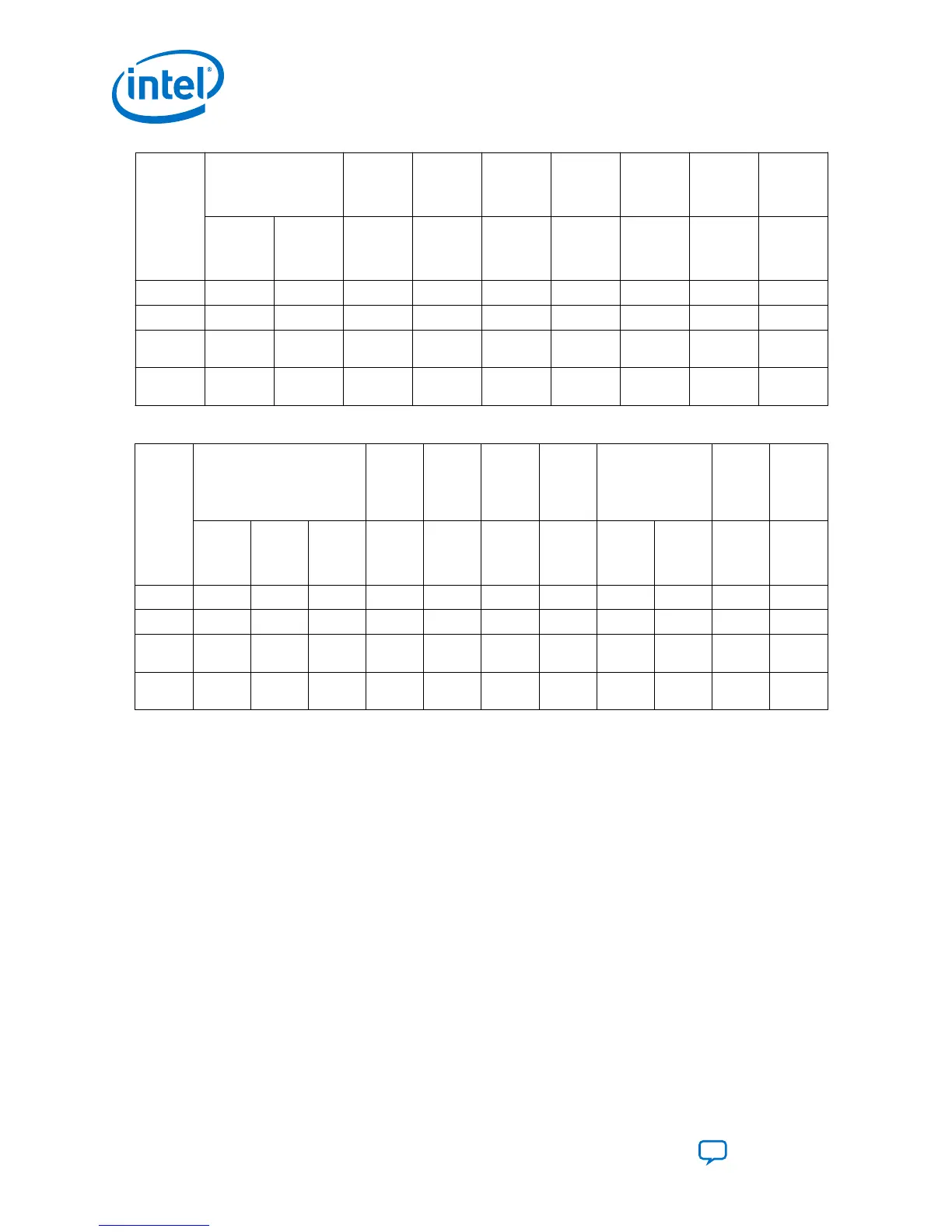

Table 37. Supported Register Configurations For FP16 Vector Three Mode

Latency Data Input Register Adder

1st

Pipeline

Registe

r

Adder

2nd

Pipeline

Registe

r

Multipli

er 1st

Pipeline

Registe

r

Multipli

er 2nd

Pipeline

Registe

r

Adder Input

Register

Adder

Pipeline

Registe

r

Output

Registe

r

accumu

late_clk

en

fp32_ad

der_a_c

lken

fp16_m

ult_inp

ut_clke

n

accum_

pipeline

_clken

accum_

2nd_pip

eline_cl

ken

mult_pi

peline_

clken

mult_2

nd_pipe

line_clk

en

accum_

adder_c

lken

adder_i

nput_cl

ken

adder_p

l_clken

output_

clken

1 Disable Disable Disable Disable Disable Disable Disable Disable Disable Disable Enable

2 Enable Enable Enable Disable Disable Disable Disable Disable Disable Disable Enable

≥3 Enable Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Enable Enable Enable

≥4 Enable Enable Enable Disable,

enable

Disable,

enable

Disable,

enable

Enable Enable Enable Enable Enable

4.2.2. Chainout Adder

You can use the output chaining path to add results from another DSP block.

Support for certain operation modes:

• Multiply-add or multiply-subtract mode

• Vector one mode

• Vector two mode

4. Intel Agilex Variable Precision DSP Blocks Design Considerations

UG-20213 | 2019.04.02

Intel

®

Agilex

™

Variable Precision DSP Blocks User Guide

Send Feedback

72

Loading...

Loading...