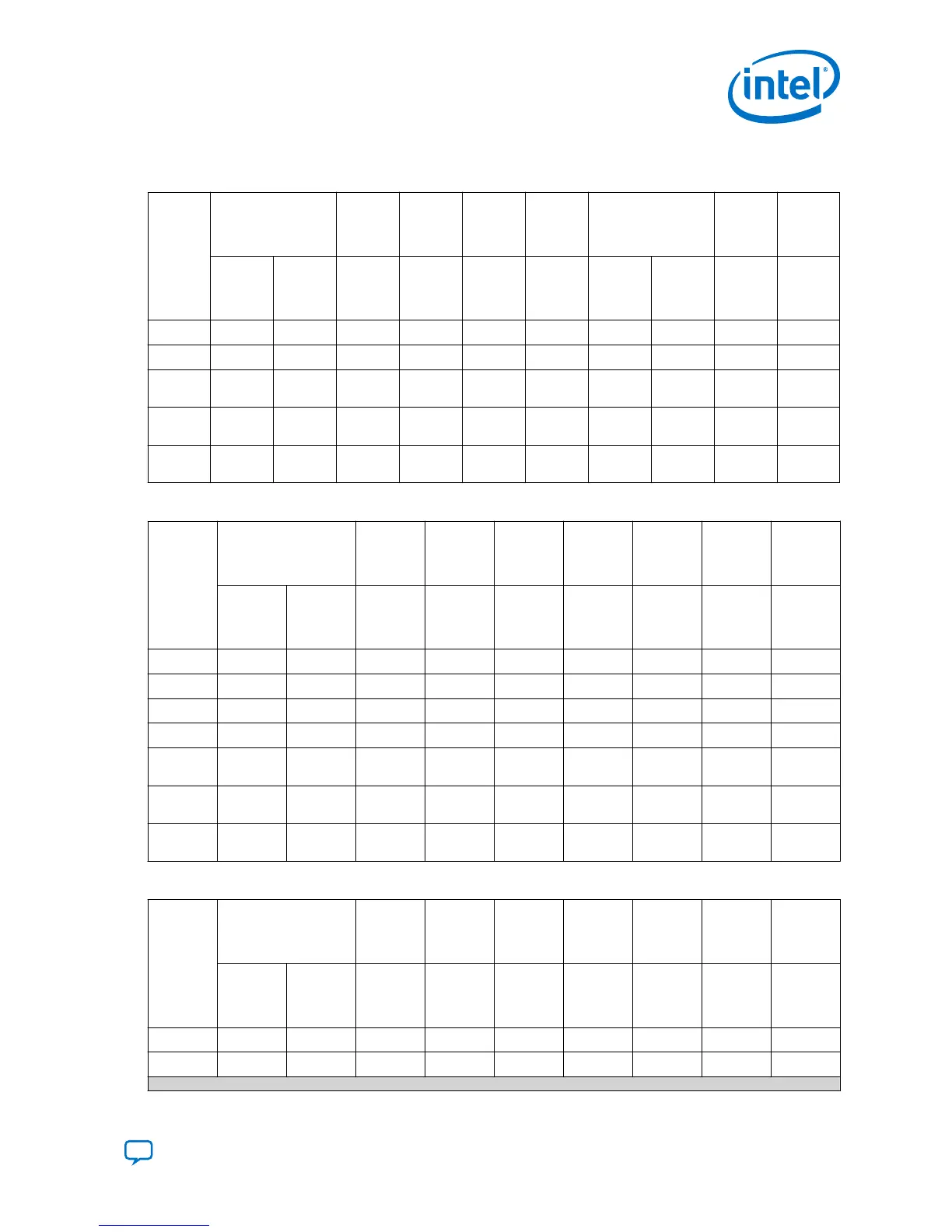

Table 34. Supported Register Configurations For Sum of Two FP16 Multiplication with

Accumulation Mode

Latency Data Input

Register

Adder

1st

Pipeline

Register

Adder

2nd

Pipeline

Register

Multiplie

r 1st

Pipeline

Register

Multiplie

r 2nd

Pipeline

Register

Adder Input

Register

Adder

Pipeline

Register

Output

Register

accumul

ate_clke

n

fp16_mu

lt_input

_clken

accum_p

ipeline_c

lken

accum_2

nd_pipel

ine_clke

n

mult_pip

eline_clk

en

mult_2n

d_pipeli

ne_clken

accum_a

dder_clk

en

adder_in

put_clke

n

adder_pl

_clken

output_c

lken

1 Disable Disable Disable Disable Disable Disable Disable Disable Disable Enable

2 Enable Enable Disable Disable Disable Disable Disable Disable Disable Enable

≥3 Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Enable Disable Enable

≥4 Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Enable Enable Enable

≥5 Enable Enable Disable,

enable

Disable,

enable

Disable,

enable

Enable Enable Enable Enable Enable

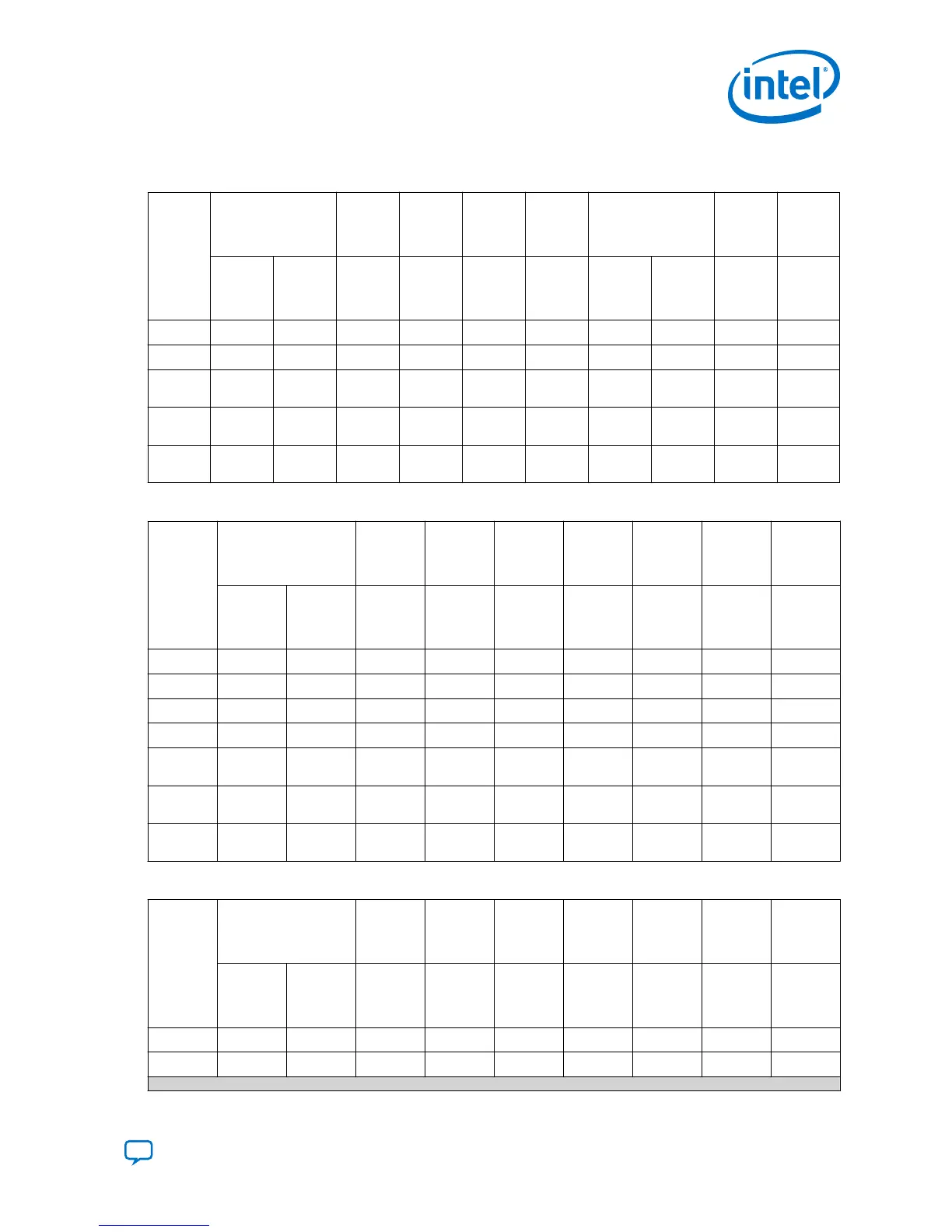

Table 35. Supported Register Configurations For FP16 Vector One Mode

Latency Data Input Register Adder 1st

Pipeline

Register

Adder

2nd

Pipeline

Register

Multiplier

1st

Pipeline

Register

Multiplier

2nd

Pipeline

Register

Adder

Input

Register

Adder

Pipeline

Register

Output

Register

fp32_add

er_a_clke

n

fp16_mul

t_input_c

lken

fp32_add

er_a_chai

nin_pl_cl

ken

fp32_add

er_a_chai

nin_2nd_

pl_clken

mult_pipe

line_clke

n

mult_2nd

_pipeline

_clken

adder_inp

ut_clken

adder_pl_

clken

output_cl

ken

0 Disable Disable Disable Disable Disable Disable Disable Disable Disable

1 Enable Enable Disable Disable Disable Disable Disable Disable Disable

1 Disable Disable Disable Disable Disable Disable Disable Disable Enable

2 Enable Enable Disable Disable Disable Disable Disable Disable Enable

≥3 Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Disable Enable

≥4 Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Enable Enable

≥5 Enable Enable Disable,

enable

Disable,

enable

Disable,

enable

Disable,

enable

Enable Enable Enable

Table 36. Supported Register Configurations For FP16 Vector Two Mode

Latency Data Input Register Adder 1st

Pipeline

Register

Adder

2nd

Pipeline

Register

Multiplier

1st

Pipeline

Register

Multiplier

2nd

Pipeline

Register

Adder

Input

Register

Adder

Pipeline

Register

Output

Register

fp32_add

er_a_clke

n

fp16_mul

t_input_c

lken

fp32_add

er_a_chai

nin_pl_cl

ken

fp32_add

er_a_chai

nin_2nd_

pl_clken

mult_pipe

line_clke

n

mult_2nd

_pipeline

_clken

adder_inp

ut_clken

adder_pl_

clken

output_cl

ken

0 Disable Disable Disable Disable Disable Disable Disable Disable Disable

1 Enable Enable Disable Disable Disable Disable Disable Disable Disable

continued...

4. Intel Agilex Variable Precision DSP Blocks Design Considerations

UG-20213 | 2019.04.02

Send Feedback

Intel

®

Agilex

™

Variable Precision DSP Blocks User Guide

71

Loading...

Loading...