•

When the pipeline registers for LOADCONST or ACCUMULATE signals are enabled,

the pipeline registers for all the multiplier inputs must be enabled and use the

same clock enable settings.

•

Disable the pipeline registers for LOADCONST or ACCUMULATE signals if these

signals are driven by a constant value.

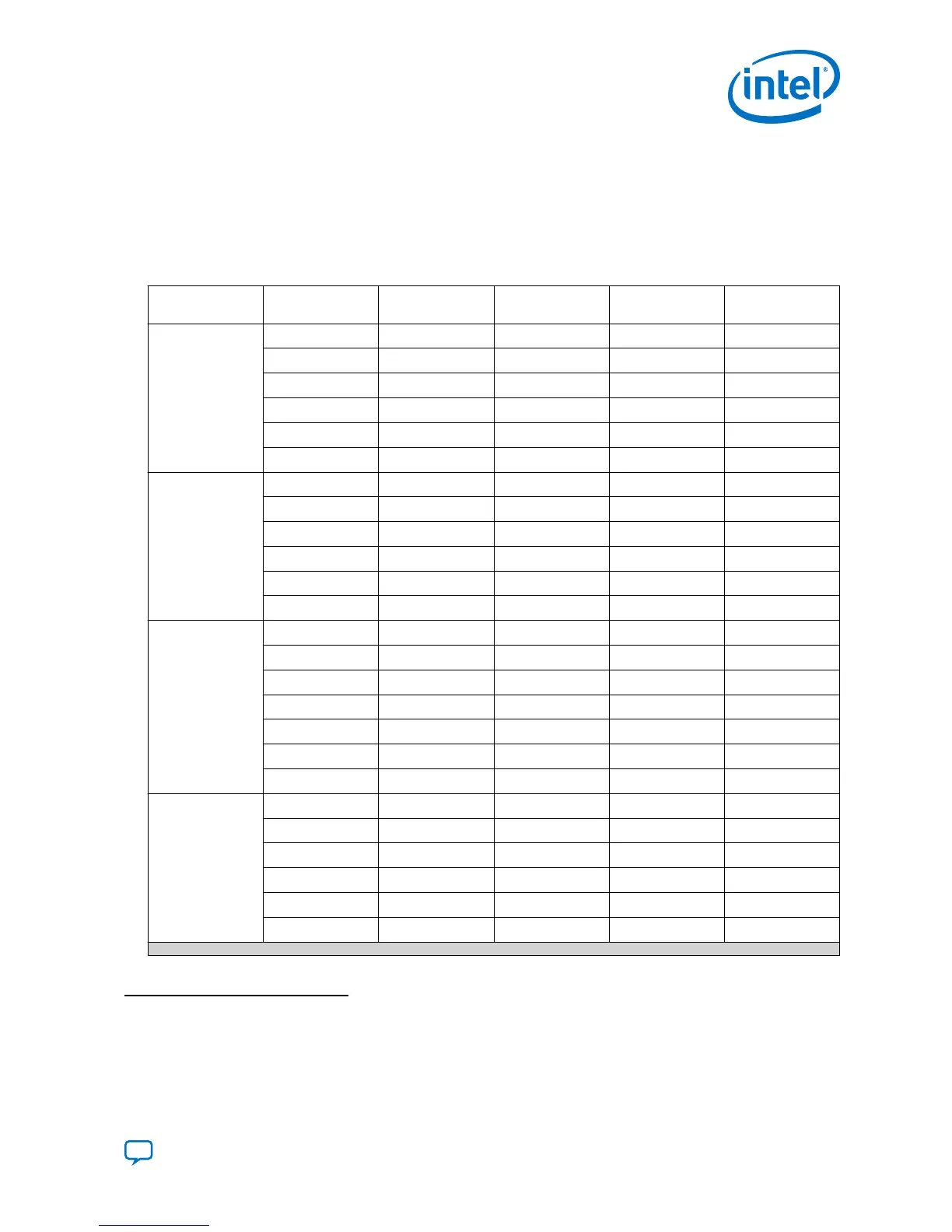

Table 24. Supported Register Configurations per Operation Modes

Operation Mode Register Level Input Register Pipeline Register 2nd Pipeline

Register

Output Register

9 x 9 Sum of 4

Mode

0 Disable Disable Disable Disable

1 Enable Disable Disable Disable

1

(5)

Disable Disable Disable Enable

2 Enable Disable Disable Enable

3 Enable Disable Enable Enable

4 Enable Enable Enable Enable

Independent

18 x 19

multiplication

0 Disable Disable Disable Disable

1 Enable Disable Disable Disable

2 Enable Disable Disable Enable

3

(6)

Enable Enable Disable Enable

3

(7)

Enable Disable Enable Enable

4 Enable Enable Enable Enable

Two 18 x 19

multiplier adder

mode

0 Disable Disable Disable Disable

1 Enable Disable Disable Disable

1

(5)

Disable Disable Disable Enable

2 Enable Disable Disable Enable

3

(6)

Enable Enable Disable Enable

3

(7)

Enable Disable Enable Enable

4 Enable Enable Enable Enable

18 x 18 multiplier

adder summed

with 36-bit input

0 Disable Disable Disable Disable

1 Enable Disable Disable Disable

1

(5)

Disable Disable Disable Enable

2 Enable Disable Disable Enable

3 Enable Disable Enable Enable

4 Enable Enable Enable Enable

continued...

(5)

When Accumulator and/or Output Chainin are enabled

(6)

When Pre-Adder and/or Coefficient are enabled

(7)

When Pre-Adder and/or Coefficient are disabled

4. Intel Agilex Variable Precision DSP Blocks Design Considerations

UG-20213 | 2019.04.02

Send Feedback

Intel

®

Agilex

™

Variable Precision DSP Blocks User Guide

63

Loading...

Loading...