Electrical

18 Design Guide

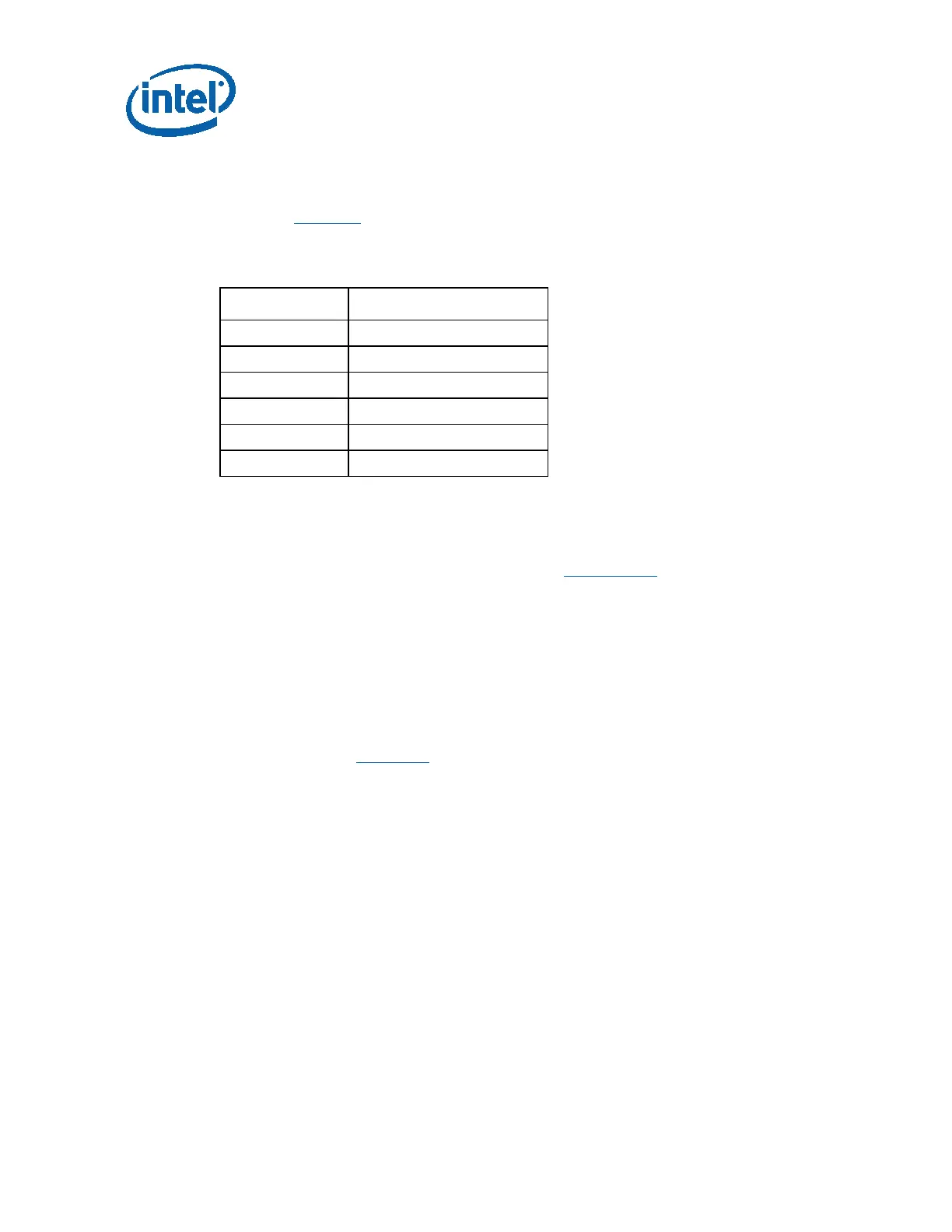

3.2.6 Capacitive Load – Recommended

The power supply should be able to power up and operate within the regulation limits

defined in Table 3-2

, with the following capacitances simultaneously present on the DC

outputs.

Table 3-6: Output Capacitive Loads

Output Capacitive Load (μF)

+12V1DC 3,300

+12V2DC 3,300

+5VDC 3,300

+3.3VDC 3,300

-12VDC 330

+5VSB 3,300

3.2.7 Closed Loop Stability - Required

The power supply shall be unconditionally stable under all line/load/transient load

conditions including capacitive loads specified in Section 3.2.6

. A minimum of 45

degrees phase margin and 10 dB gain margin is recommended at both the maximum

and minimum loads.

3.2.8 +5V DC / +3.3V DC Power Sequencing - Required

The +12V1 DC / +12V2 DC and +5 VDC output levels must be equal to or greater

than the +3.3 VDC output at all times during power-up and normal operation. The

time between any output of +12V1 DC / +12V2 DC and +5 VDC reaching its minimum

in-regulation level and +3.3 VDC reaching its minimum in-regulation level must be ≤

20 ms as shown in Figure 3-2

.

Loading...

Loading...