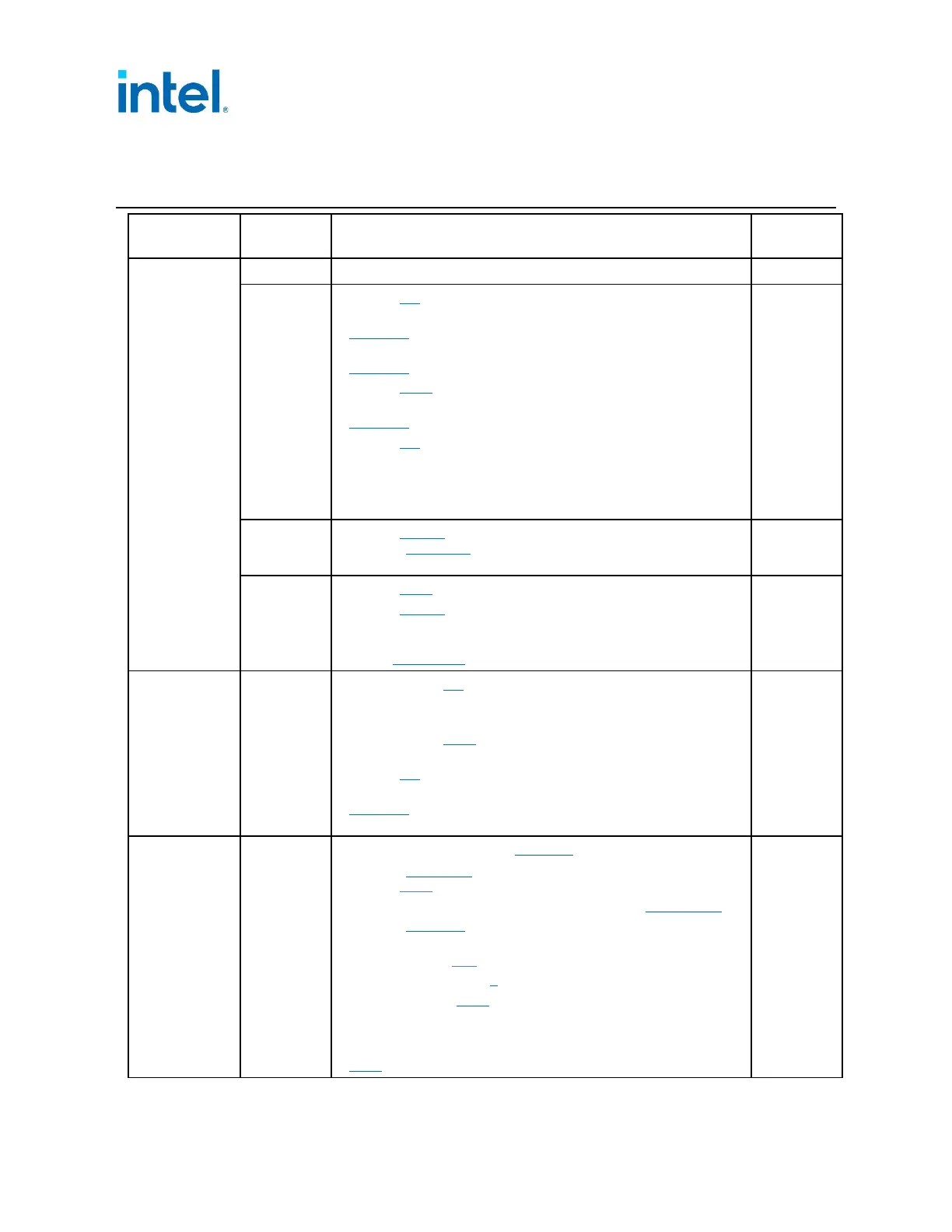

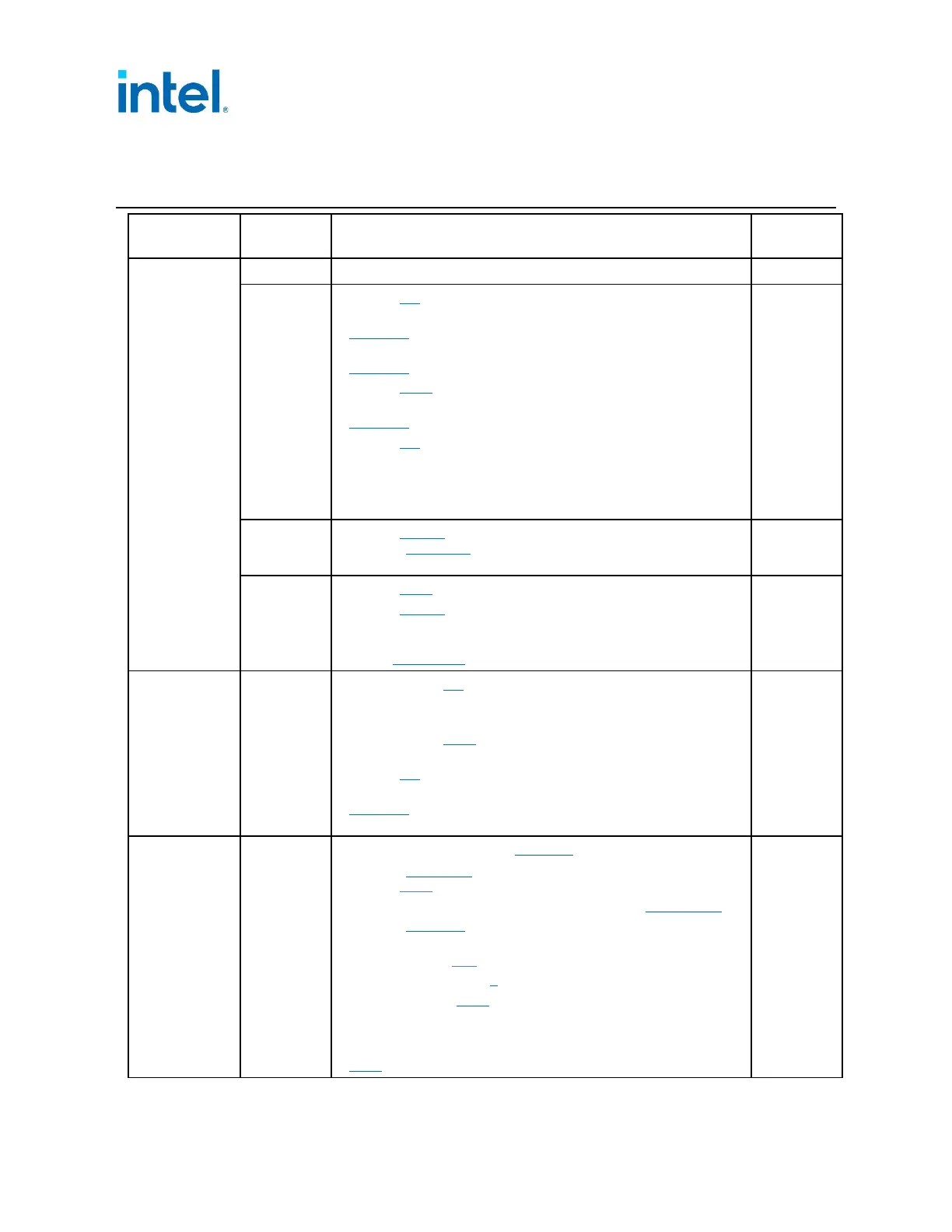

8 613768

Revision History

Document

Number

Revision

Number

Description

Revision

Date

613768

0.9

• Initial version

May 2019

1.0

• Section 2.1

– Added reference of PSU Addendum for all future

processor support.

• Table 4-6 – Updated 12VSB Ripple and Noise p-pV value to

match all other 12V Rails.

• Table 4-8 – Added note of where T0 is referenced.

• Section 4.5.9– Updated link of current ENERGY STAR*

Computers specification to version 8.0.

• Table 5-1 – Updated pin 10.

• Section 5.3 – Explained 4 pin and 6 pin SATA Power

connection in detail

• Changed all wording for Alternative Sleep Mode to Alternative

Low Power Mode (Although they both reference the same

power state, ALPM is more generic).

May 2020

1.01

• Section 5.2.2.1

– Updated the part number for CviLux*.

Updated Figure 5-3 to provide more clarification on the

connector.

November

2020

1.02

• Section 4.2.3

– Added extra clarity for use of remote sensing

• Section 5.2.2.1 – Updated the part number for Lotes*.

Provided clarification about Remote Sensing for the

connector.

• Added Figure 14-7 (Different Fan Option for SFX form factor)

February

2021

613768 1.1

• Added Section 1.2

– System Power Telemetry Feature

• Table 4-17 – Low Load Efficiency previous required levels

moved to recommended and new required level is added

• Added Section 4.3.7

– System Power (Psys) entire section is

new

• Section 5.1 – Label of all PSUs should state revision of the

specification that it meets

• Table 5-2: Main Power Connector Pinout – Pin 5 is now

defined

March

2022

613768 2.0

• Updated text for clarity in Section 1

: Introduction

• Updated Section1.1 added second reference for ALPM in

Section 4.3.2

• Added new Reference Documentations to list in Section 1.3

• Updated Table 2-1: Processor Configurations – 12V2 Current

and reference text for Processors

• Updated Section 2.2 for accuracy and clarity

• Added ALL of Chapter 3 – PCIe* AIC Consideration

• Updated Section 4.2.1 and Table 4-2 - DC Voltage lower

voltage range is changed to 11.2 Volts.

• Updated DC Output current – Slew rate is increased to meet

PCIe CEM requirements, along with max step size Section

4.2.2

March

2022

Loading...

Loading...