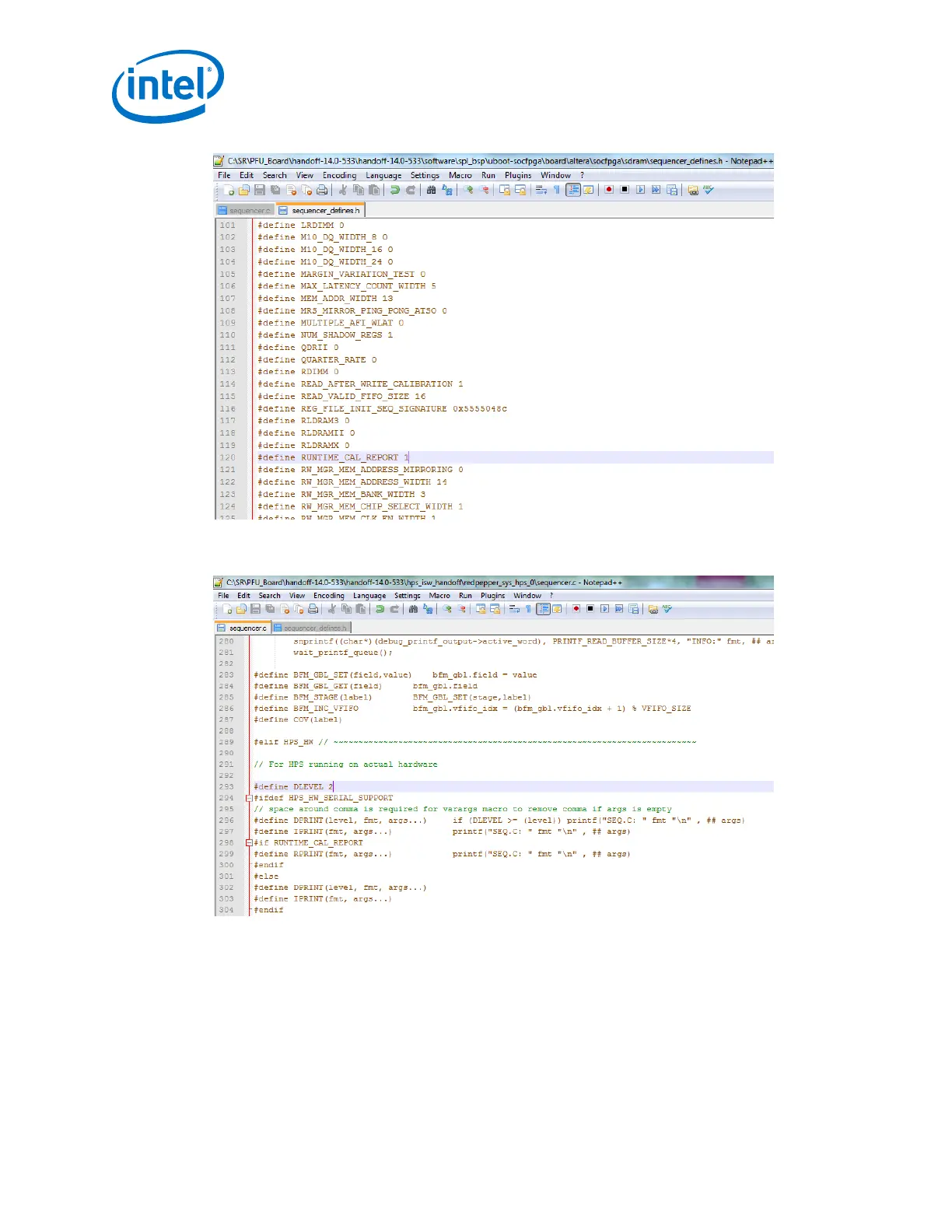

5.4.1.2. Change DLEVEL To Get More Debug Information

5.4.1.3. Enable Example Driver for HPS SDRAM

• Enable with Hardware Diagnostic Option in bsp-editor. Note: Example driver is

only available in Intel Quartus Prime version 14.0 and later.

— PRBS31 Data pattern

— Write to random address => Read from random address

— Can select different coverage by changing parameter in spl.c

5. Embedded Software Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

64

Loading...

Loading...