147

LCD PC E

LCD PC E

-

-

8590 MAINTENANCE

8590 MAINTENANCE

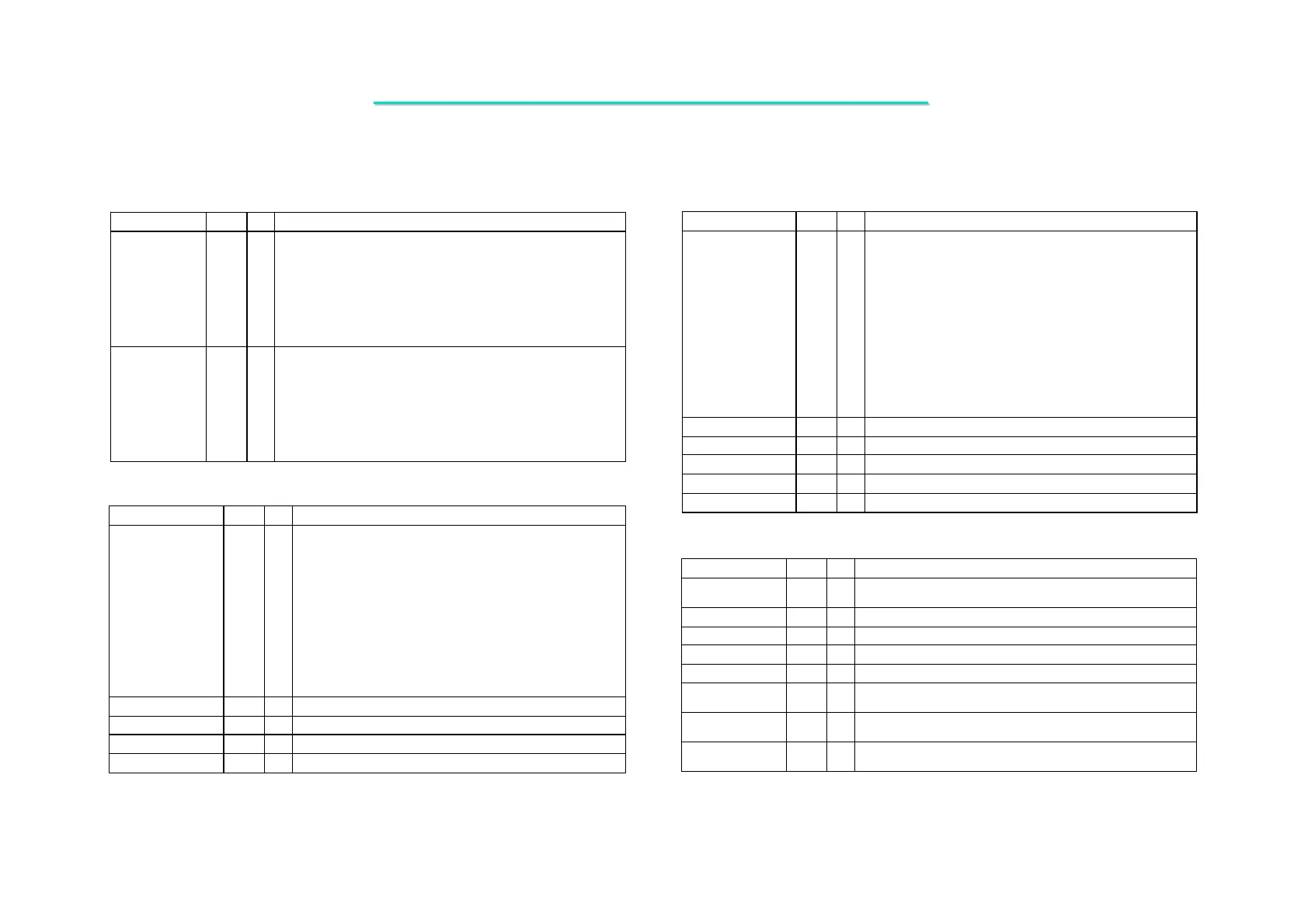

SMB / I2C Interface

Signal Name Pin # I/O Signal Description

SPCLK[2:1]

E9, C9

IO

Serial Port (SMB/I2C) Clocks.

These are the clocks for serial data

transfer. SPCLK1 is typically used for I2C communications. As an

output, it is programmed via CRA0[0]. As an input, its status is read

via CRA0[2]. In either case the serial port must be enabled by

CRA0[4] = 1. SPCLK2 is typically used for DDC monitor

communications. As an output, it is programmed via CRB1[0]. As an

input, its status is read via CRB1[2]. The port is enabled via

CRB1[4] = 1.

SPDAT[2 :1]

E8, D9

IO

Serial Port (SMB/I2C) Data.

These are the data signals used for

serial data transfer.SPDAT1 is typically used for I2C

communications. As an output, it is programmed via CRA0[1]. As an

input, its status is read via CRA0[3]. In either case the serial port

must be enabled by CRA0[4] = 1. SPDAT2 is typically used for

DDC monitor communications. As an output, it is programmed via

CRB1[1]. As an input, its status is read via CRB1[3]. The port is

enabled via CRB1[4] = 1.

Flat Panel Monitor (DVI) Interface

Signal Name Pin # I/O

Signal Description

FPD11

/ TVBL#,

FPD10

/ TVD10,

FPD9 / TVD 9/ strap,

FPD8

/ TVD 8,

FPD7 / TVD 7/ strap,

FPD6

/ TVD 6/ strap,

FPD5

/ TVD 5/ strap,

FPD4 / TVD 4/ strap,

FPD3

/ TVD 3/ strap,

FPD2 / TVD 2/ strap,

FPD1

/ TVD 1/ strap,

FPD0

/ TVD 0/ strap

A11

B11

E12

B12

A12

C12

D12

E13

D13

A13

B13

C13

O

Panel Data.

8mA is the default. 16mA is selected via

SR3D[6]=1. This function is selected on these pins when

SR31[4] = 1.

FPCLK / TVCLKO E11 O Panel Clock. 8mA is the default. 16mA may also be selected.

FPHS / TVHS D10 O

Panel Horizontal Sync.

FPVS / TVVS C10 O

Panel Vertical Sync.

FPDE / TVCLKI B10 O

Panel Data Enable.

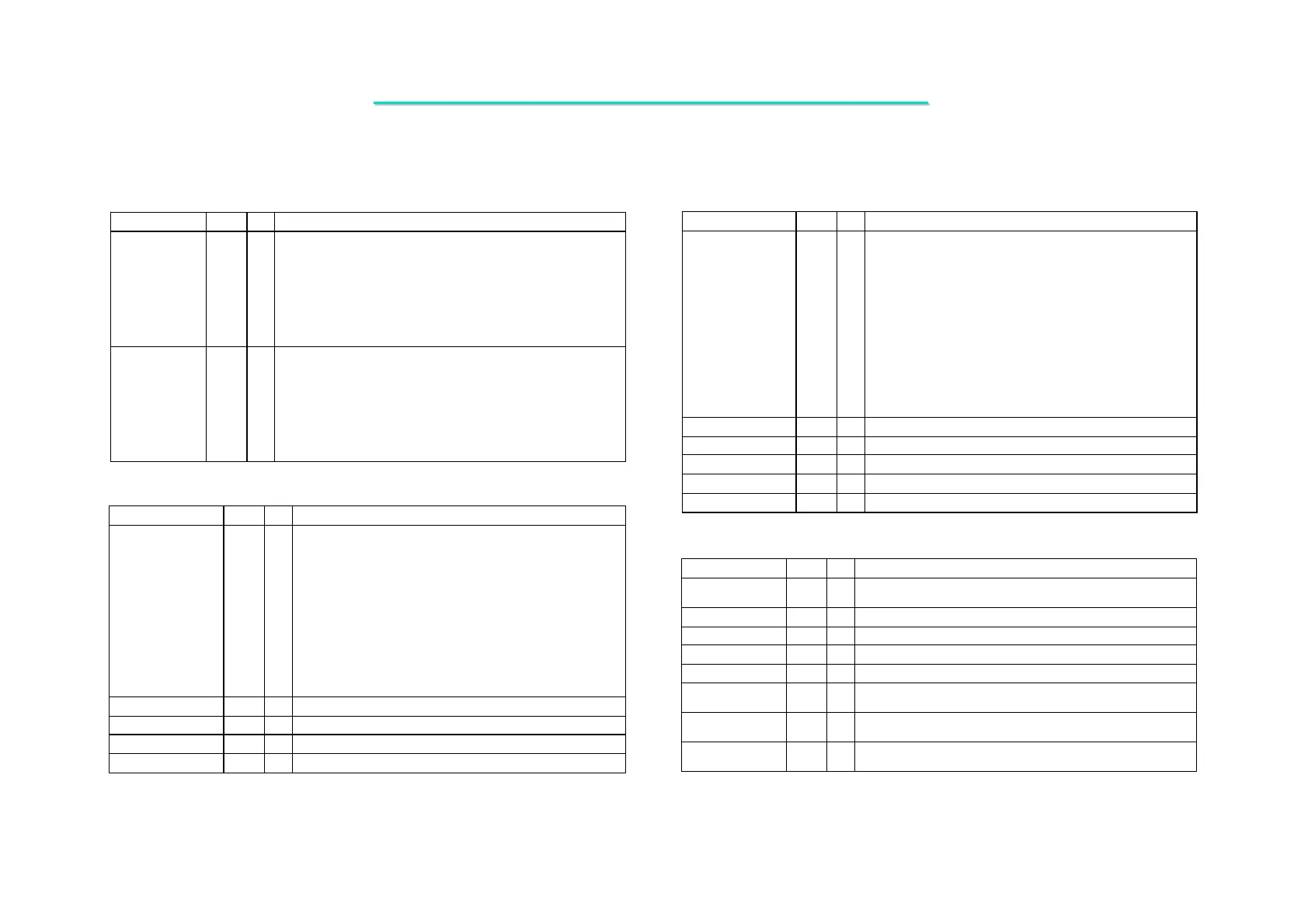

TV Encoder Interface

Signal Name Pin # I/O Signal Description

TVD11

/ FPDET,

TVD10

/ FPD10,

TVD9 / FPD9 / strap,

TVD8

/ FPD8,

TVD7 / FPD7 / strap,

TVD6

/ FPD6 / strap,

TVD5

/ FPD5 / strap,

TVD4 / FPD4 / strap,

TVD3

/ FPD3 / strap,

TVD2 / FPD2 / strap,

TVD1

/ FPD1 / strap,

TVD0

/ FPD0 / strap

A10

B11

E12

B12

A12

C12

D12

E13

D13

A13

B13

C13

O

TV Encoder Output Data.

TVCLKI

/ FPDE B10 I

TV Encoder Clock In.

Input clock from encoder.

TVCLKO

/ FPCLK E11 O

TV Encoder Clock Out.

Output clock to TV encoder.

TVHS

/ FPHS D10 O

TV Encoder HSYNC.

TVVS

/ FPVS C10 O

TV Encoder VSYNC.

TVBL#

/ FPD11 A11 O

TV Encoder Blanking.

Flat Panel Interface

Signal Name Pin # I/O Signal Description

PD[35:0]

O

Panel Data. Default output drive is 8 mA. 16mA may be selected

via SR3D[6]=1.

PANELCLK

R02 O

Panel Clock.

8mA is the default. 16mA may also be selected.

PANELHS

V02 O

Panel Horizontal Sync.

PANELVS

V01 O

Panel Vertical Sync.

PANELDE

U01 O

Panel Data Enable.

PANELDET

B01

I

Panel Detect.

If SR30[1]=0, SR30[2] will read 1 if a Flat Panel is

properly connected. Must be tied to ground if not used.

ENVDD

D02

O

Enable VDD. This signal is driven high to external logic to initiate

a flat panel power up sequence.

ENVEE

D01

O

Enable VEE.

This signal is driven high to a programmable time

after ENVDD is driven high during a flat panel power up sequence.

5.2 VIA VT8703 North Bridge with S3 Savage4 AGPX4

Loading...

Loading...