473

APPENDICES

A

Appendix 3 CPU Module Processing Time

Appendix 3.2 Time required for each processing included in scan time

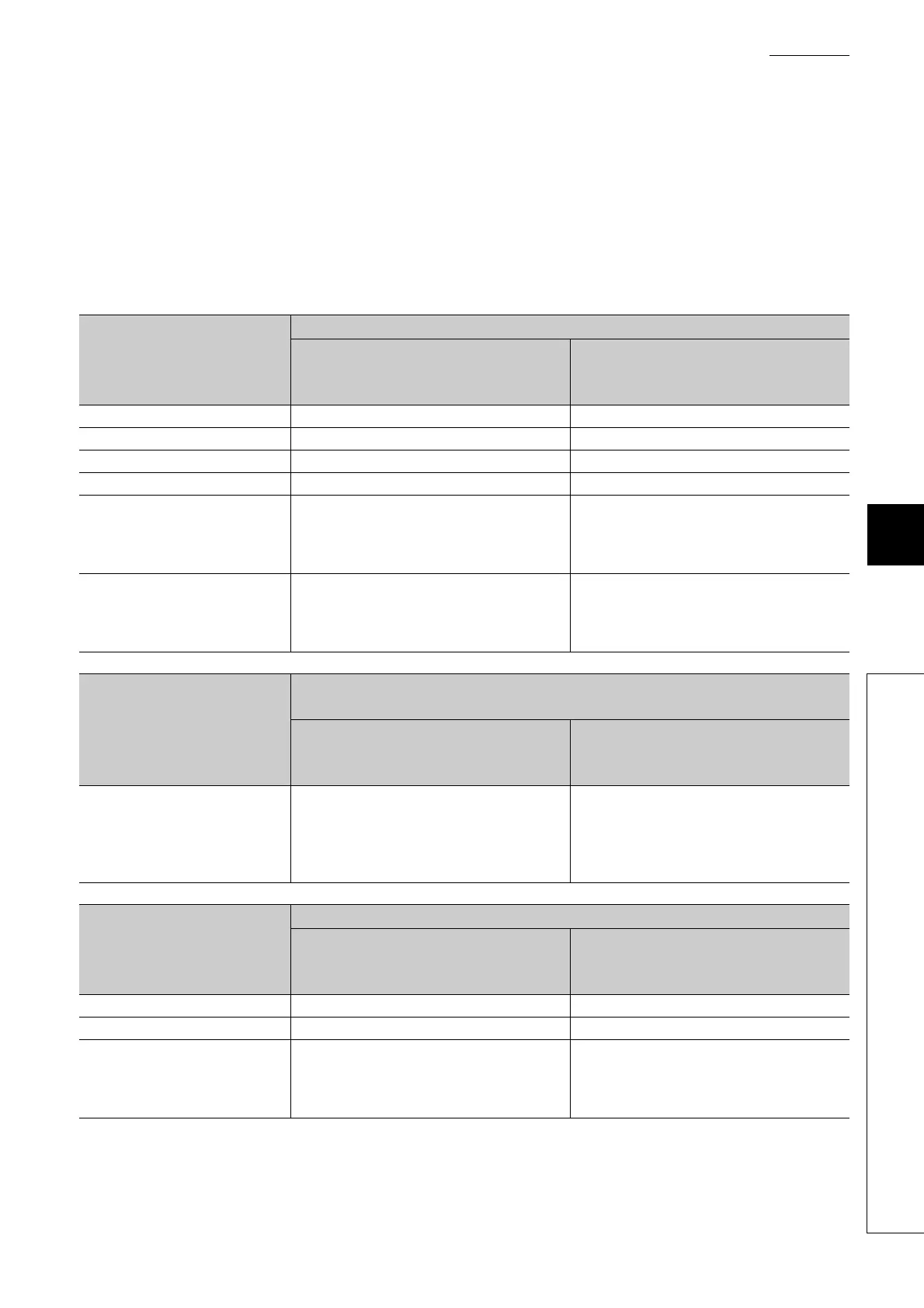

(d) Overhead time when local devices in the interrupt program are enabled

When SM777 (Enable/disable local device in interrupt program) turns on, the time given in the following tables

will be added to the overhead time given in Page 471, Appendix 3.2 (3) (a). Each n, N1, N2, and N3 in the table

indicates the following.

• n: Number of local device points (unit: K words)

• N1: Number of devices that specified a local device

• N2: Number of word device points that specified a local device

• N3: Number of bit device points that specified a local device

CPU module

When a local device file in the standard RAM is used

Additional time to the pre-start overhead time

for interrupt programs

(Page 471,

Appendix 3.2 (3) (a))

Additional time to the program-end overhead

time for interrupt programs

(Page 472,

Appendix 3.2 (3) (b))

Q00UCPU, Q01UCPU (13.2 × N1) + (0.22 × (N2 + (N3 16))) + 210µs (8 × N1) + (0.23 × (N2 + (N3 16))) + 30µs

Q02UCPU

(13.2 × N1) + (0.22 × (N2 + (N3 16))) + 210µs (8 × N1) + (0.22 × (N2 + (N3 16))) + 30µs

Q03UD(E)CPU

(8 × N1) + (0.22 × (N2 + (N3 16))) + 80µs (8 × N1) + (0.22 × (N2 + (N3 16))) + 20µs

Q03UDVCPU

(4.1 × N1) + (0.165 × (N2 + (N3 16))) + 22.0µs (4.1 × N1) + (0.165 × (N2 + (N3 16))) + 5.7µs

Q04UD(E)HCPU, Q06UD(E)HCPU,

Q10UD(E)HCPU, Q13UD(E)HCPU,

Q20UD(E)HCPU, Q26UD(E)HCPU,

Q50UDEHCPU, Q100UDEHCPU

(8 × N1) + (0.10 × (N2 + (N3 16))) + 80µs (8 × N1) + (0.10 × (N2 + (N3 16))) + 20µs

Q04UDVCPU, Q04UDPVCPU,

Q06UDVCPU, Q06UDPVCPU,

Q13UDVCPU, Q13UDPVCPU,

Q26UDVCPU, Q26UDPVCPU

(4.0 × N1) + (0.085 × (N2 + (N3 16))) + 22.0µs (4.0 × N1) + (0.085 × (N2 + (N3 16))) + 5.7µs

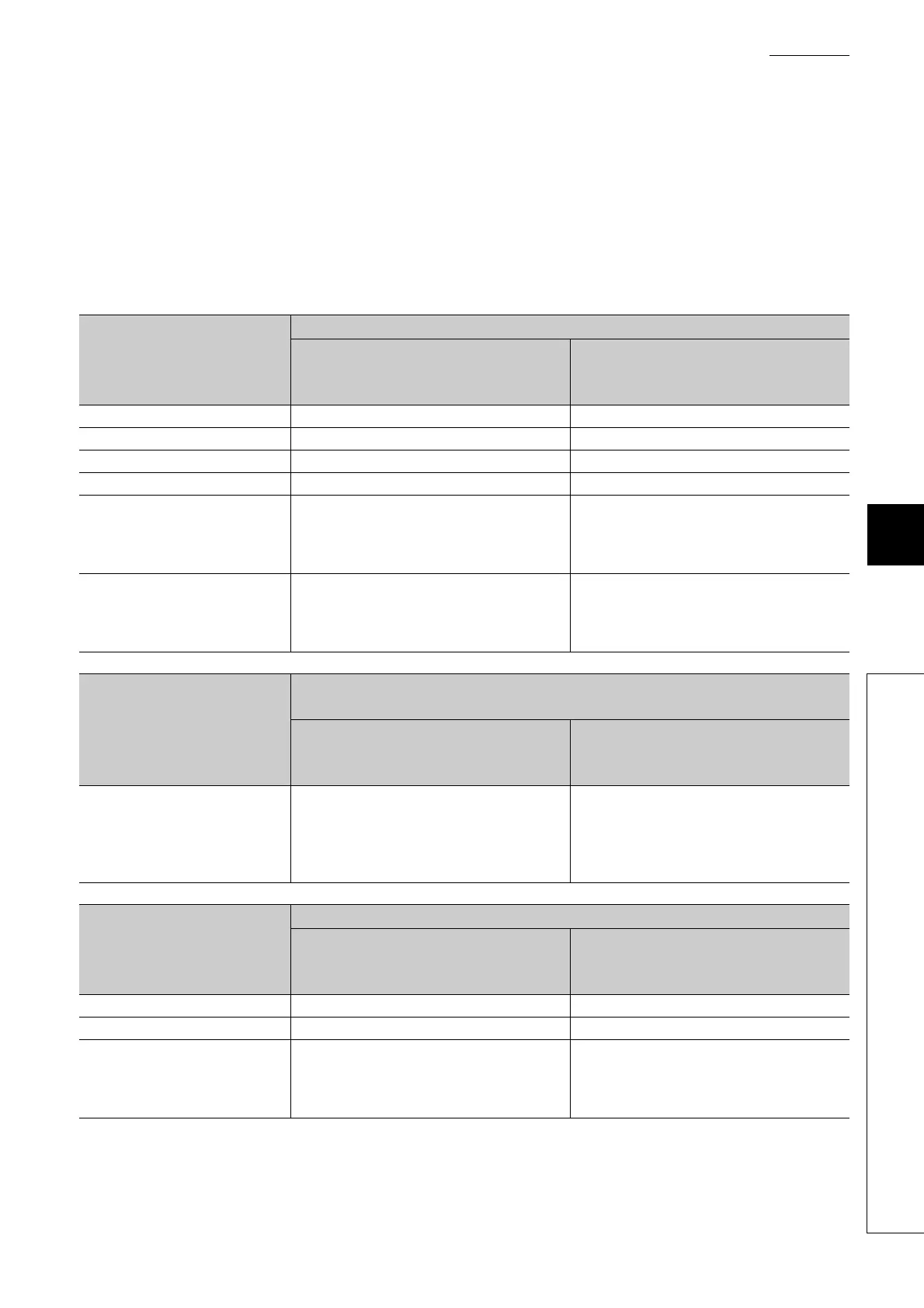

CPU module

When a local device file in the standard RAM is used

(with an extended SRAM cassette)

Additional time to the pre-start overhead time

for interrupt programs

(Page 471,

Appendix 3.2 (3) (a))

Additional time to the program-end overhead

time for interrupt programs

(Page 472,

Appendix 3.2 (3) (b))

Q03UDVCPU, Q04UDVCPU,

Q04UDPVCPU, Q06UDVCPU,

Q06UDPVCPU, Q13UDVCPU,

Q13UDPVCPU, Q26UDVCPU,

Q26UDPVCPU

(4.2 × N1) + (0.220 × (N2 + (N3 16))) + 22.0µs (4.2 × N1) + (0.220 × (N2 + (N3 16))) + 5.7µs

CPU module

When a local device file in the SRAM card is used

Additional time to the pre-start overhead time

for interrupt programs

(Page 471,

Appendix 3.2 (3) (a))

Additional time to the program-end overhead

time for interrupt programs

(Page 472,

Appendix 3.2 (3) (b))

Q02UCPU (16 × N1) + (0.43 × (N2 + (N3 16))) + 260µs (16 × N1) + (0.43 × (N2 + (N3 16))) + 60µs

Q03UD(E)CPU

(12 × N1) + (0.43 × (N2 + (N3 16))) + 100µs (12 × N1) + (0.43 × (N2 + (N3 16))) + 20µs

Q04UD(E)HCPU, Q06UD(E)HCPU,

Q10UD(E)HCPU, Q13UD(E)HCPU,

Q20UD(E)HCPU, Q26UD(E)HCPU,

Q50UDEHCPU, Q100UDEHCPU

(12 × N1) + (0.40 × (N2 + (N3 16))) + 100µs (12 × N1) + (0.40 × (N2 + (N3 16))) + 20µs

Loading...

Loading...