543

APPENDICES

A

Appendix 5 Replacing Basic Model QCPU or Qn(H)CPU with QnUCPU

Appendix 5.4 Functions

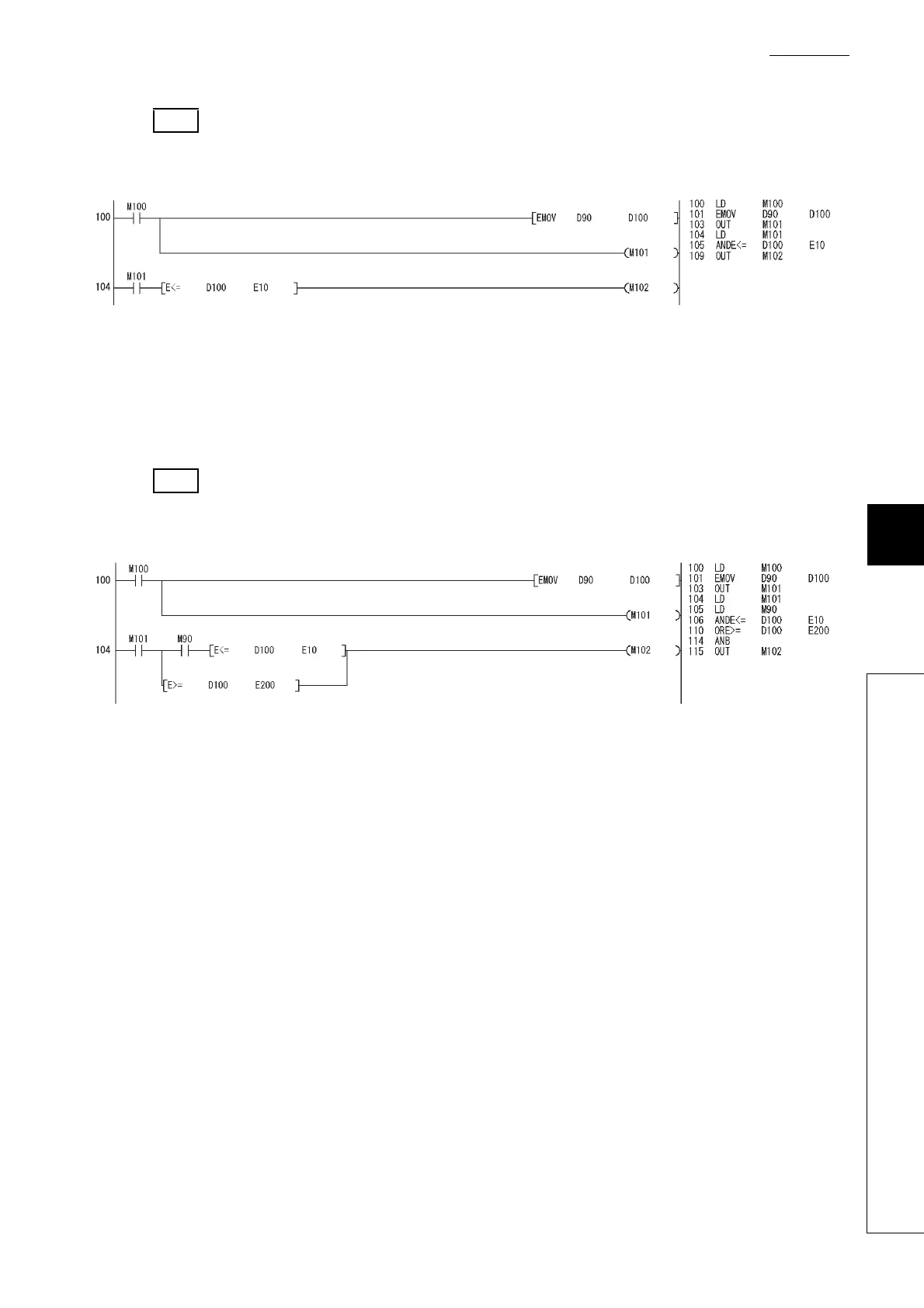

[Ladder mode] [List mode]

In the ladder block starting from the step 104, the ANDE<= instruction of the step 105 is not executed when the

M101 (valid data flag) is off.

The ANDE<= instruction of the step 105 is not executed when the M101 is off in the LD instruction of the step 104

in the program above. Therefore, when the M101 is off, "OPERATION ERROR" (error code: 4140) will not be

detected even if a "special value" is stored in D100.

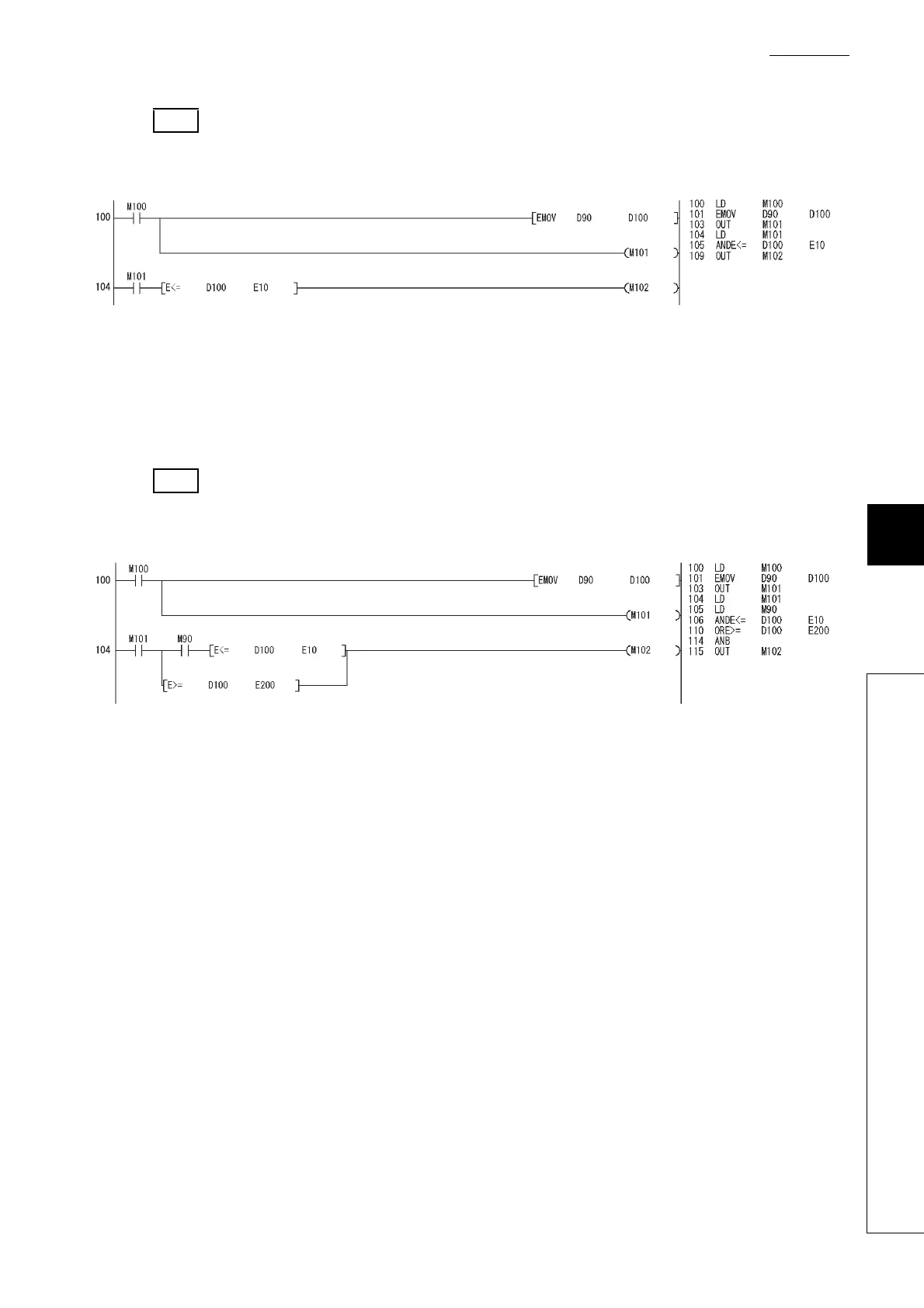

[Ladder mode] [List mode]

In the ladder block starting from the step 104, the ANDE<= instruction of the step 106 and the ORE>= instruction

of the step 110 are not executed when the M101 (valid data flag) is off.

However, if the M90 is on in the LD instruction of the step 105, the ANDE<= instruction of the step 106 is

executed. Therefore, even when the M101 is off, "OPERATION ERROR" (error code: 4140) will be detected in

the ANDE<= instruction of the step 106 if the M90 is on and a "special value" is stored in D100.

For the method of avoiding "OPERATION ERROR", refer to Page 544, Appendix 5.4.2 (2).

Ex.2)

Not detecting "OPERATION ERROR" (error code: 4140) in the ANDE instruction

Ex.3)

Detecting "OPERATION ERROR" (error code: 4140) in the ANDE instruction

Loading...

Loading...