270

XCH, XCHP, DXCH, DXCHP

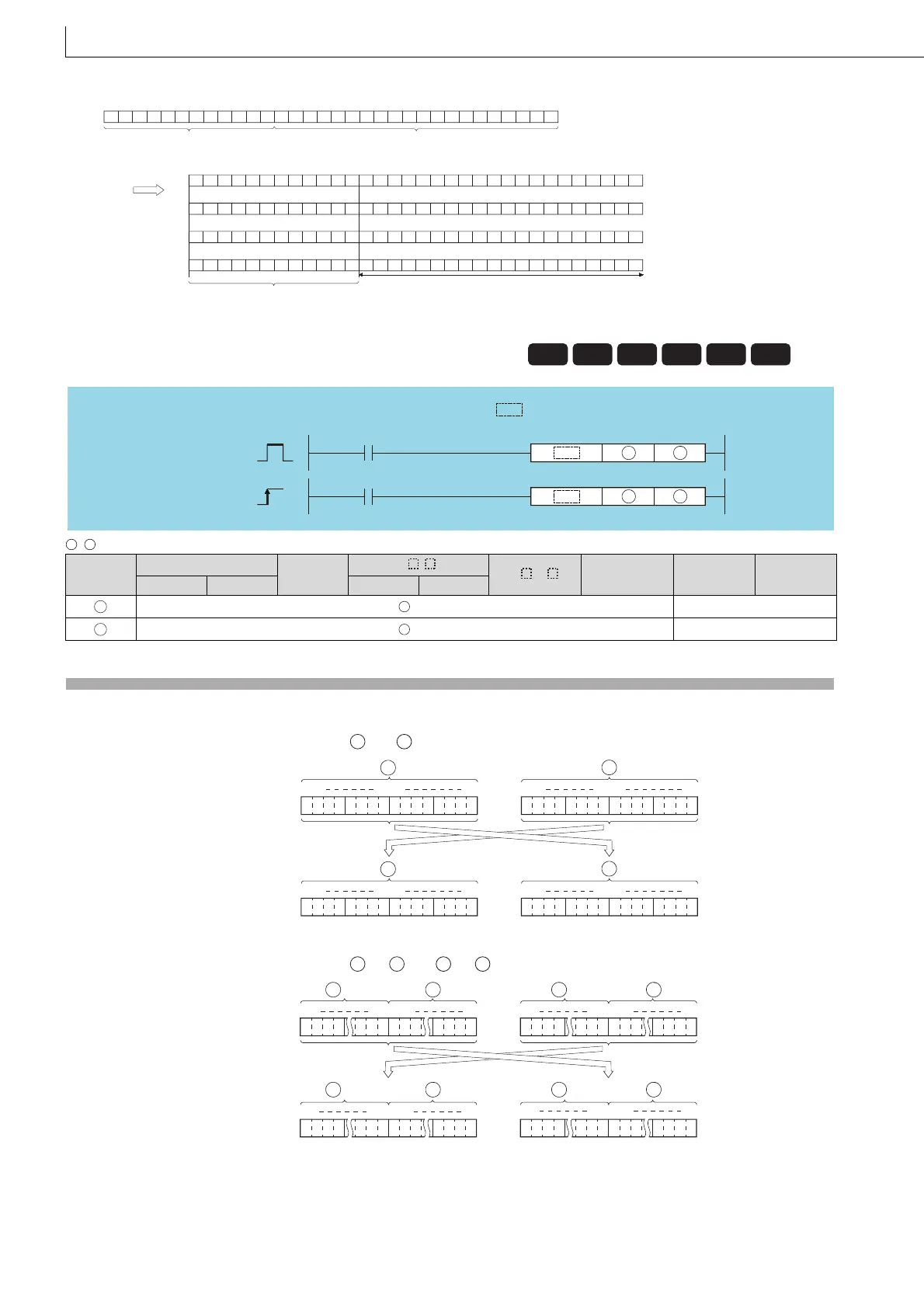

[Operation]

, : Head number of the devices where the data to be exchanged is stored (BIN 16/32 bits)

Function

XCH

(1) Conducts 16-bit data exchange between and .

DXCH

(1) Conducts 32-bit data exchange between +1, and +1, .

6.4.9 XCH, XCHP 16-bit data ex changes

DXCH, DXC HP 32-bit data exchanges

6.4.9

XCH, XCHP, DXCH, DXCHP

Setting

Data

Internal Devices

R, ZR

J\

U\G

Zn Constants Other

Bit Word Bit Word

––

––

D11,D1

D13,D1

D15,D1

D17,D1

Transfer

1F

11

1 1 1 1 1 1 1 1 1 1 1 1 01

Y14 Y13 Y0

0 1 0 1 0 1 0 1 0 1 0 1 0101

Ignored 20 bits (five digits) data

1 1 010 1 0 1 0 1 0 1 0 1 0 1 0101

Filled with 0s

20 bits (five digits)

1 1 010 1 0 1 0 1 0 1 0 1 0 1 0101

1 1 010 1 0 1 0 1 0 1 0 1 0 1 0101

b31

00

0 0 0 0 0 0 0 0 0 0

000000000000

000000000000

000000000000

1 1 01

b20 b19 b0

0 1 0 1 0 1 0 1 0 1 0 1 0101

Basic

Process

High

performance

Redundant

Universal

LCPU

Command

Command

P

D1 D2

D1 D2

XCH, DXCH

XCHP, DXCHP

indicates an instruction symbol of XCH, DXCH.

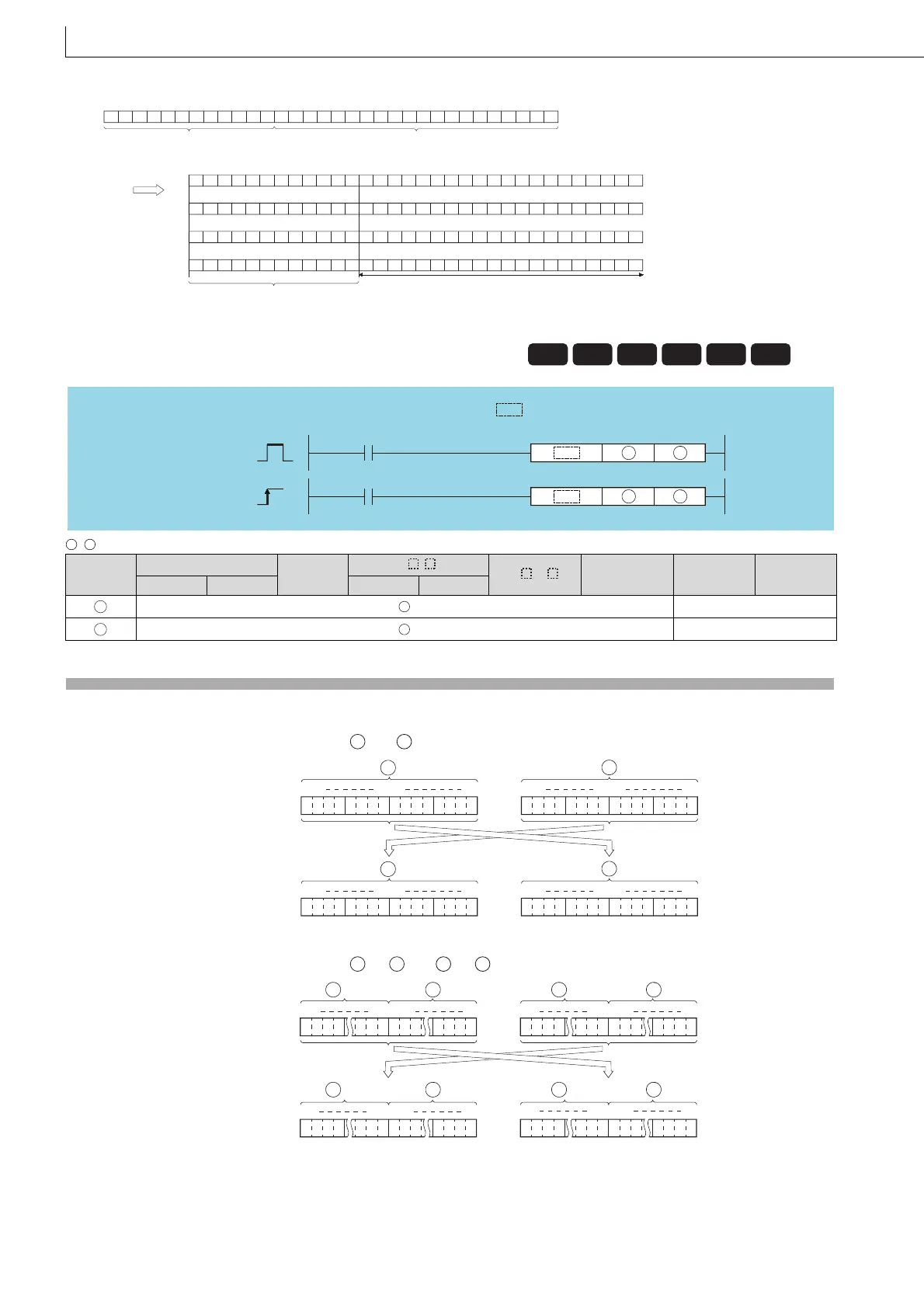

D1

D2

D1

D2

D1 D2

b7 b0b15 b8

Before execution

fter execution

00000

111

0000

111

0

1111000000001111 0000011100001110

1111

00000000

1111

D1

D

2

b7

b0b15 b8

b7

b0b15 b8b7 b0b15 b8

D1

D

2

D1 D1 D2 D2

Before execution

fter execution

+1

b15

b0

+1

b31

b16

+1+1

111 11111110000

111

0000000

1111

111 1111111

0000

111 00000001111

D1

D2

D1

b15 b0b31 b16

b15

b0b31 b16

b15 b0b31 b16

D1 D1

D2

D2

D2

Loading...

Loading...