359

ENCO, ENCOP

1

2

3

4

4

6

7

8

7.5 Data processing instructions

7.5.4 ENCO, ENCOP

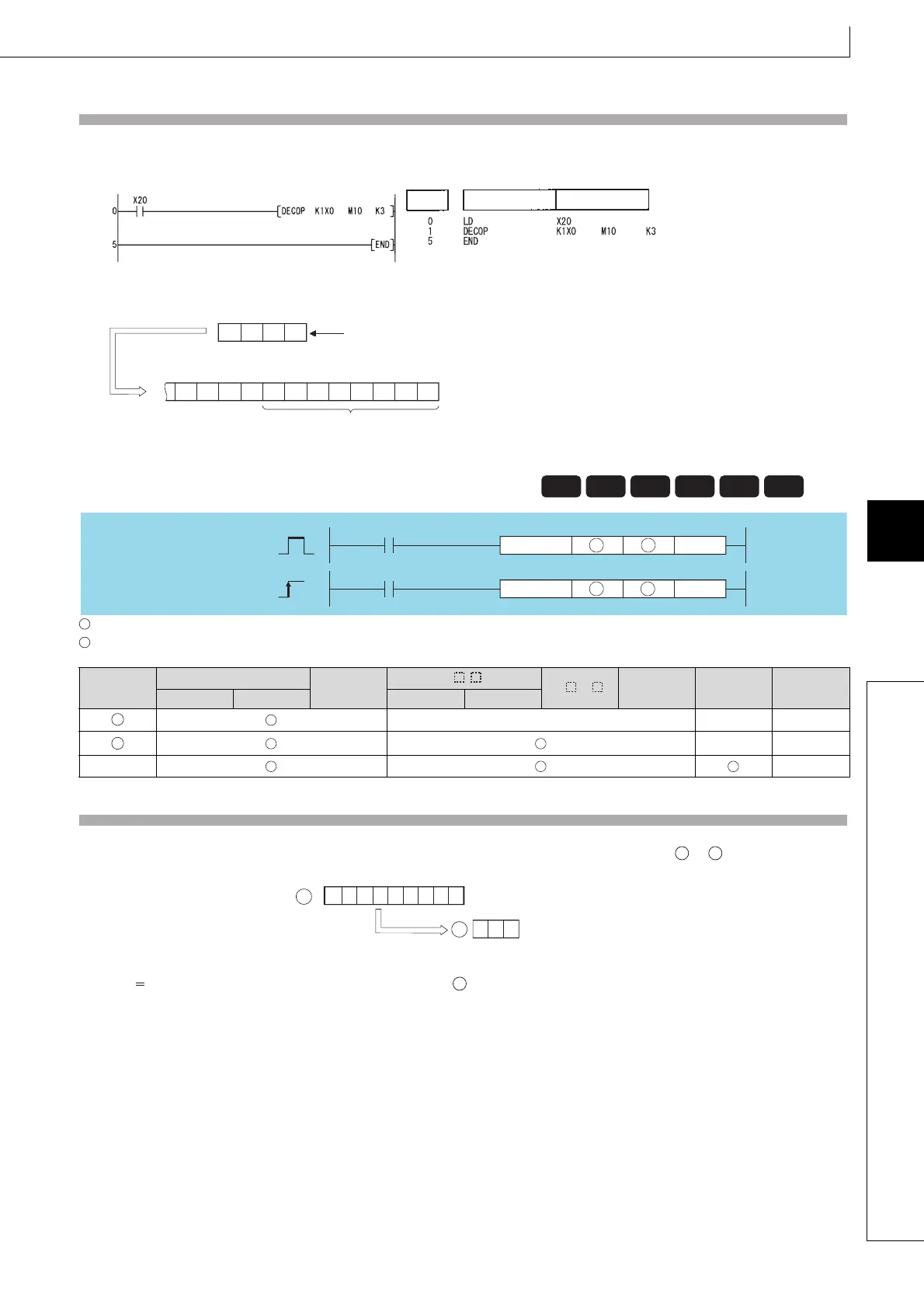

Program Example

(1) The following program decodes the 3 bits from X0 and stores the results at M10 when X20 is ON.

[Ladder Mode] [List Mode]

[Operation]

: Head number of the device where the data to be encoded is stored (Device name)

: Number of the device where the encoding result will be stored (BIN 16 bits)

n : Valid bit length (1 to 8), 0: No processing (BIN 16 bits)

Function

(1) Stores the binary value corresponding to the bits which are "1" included in the 2

n

-bit data of to .

(2) The value of n can be designated at between 1 and 8.

(3) If n 0, there will be no operation, and the contents of will not change.

(4) Bit devices are treated as 1 bit, and word devices as 16 bits.

(5) If more than 1 bit is at 1, processing will be conducted at the upper bit location.

7.5.4 ENCO, ENCOP Encodi ng from 256 to 8 bits

7.5.4

ENCO, ENCOP

Setting

Data

Internal Devices

R, ZR

J\

U\G

Zn

Constants

K, H

Other

Bit Word Bit Word

–– –– ––

–– ––

n ––

Step

Instruction

Device

0 0 0 0 01 0 0 000

M10M17

0

If 3 bits are designated as significant bits, 8 points are occupied.

Decoding result

00

11

0

X0X1X2

When 6 is designated at X0 to X2

Basic

Process

High

performance

Redundant

Universal

LCPU

n

n

ENCO

ENCOP

D

D

Command

Command

ENCOP

ENCO S

S

S

D

S

D

S

D

7

0

86

(Binary value = 6)

543210

0 1000000

110

S

D

D

Loading...

Loading...