44

*7: The number of steps may vary depending on the device and type of CPU module being used.

Note 1) When using a High Performance model QCPU, Process CPU or Redundant CPU, the number of steps increases but

the processing speed becomes faster.

Note 2) The number of steps may increase due to the conditions described in Page 110, Section 3.8.

2.4.3 Data conversion instructions

*1: The number of basic steps is two for the Universal model QCPU and LCPU only.

*2: The subset is effective only with Universal model QCPU and LCPU.

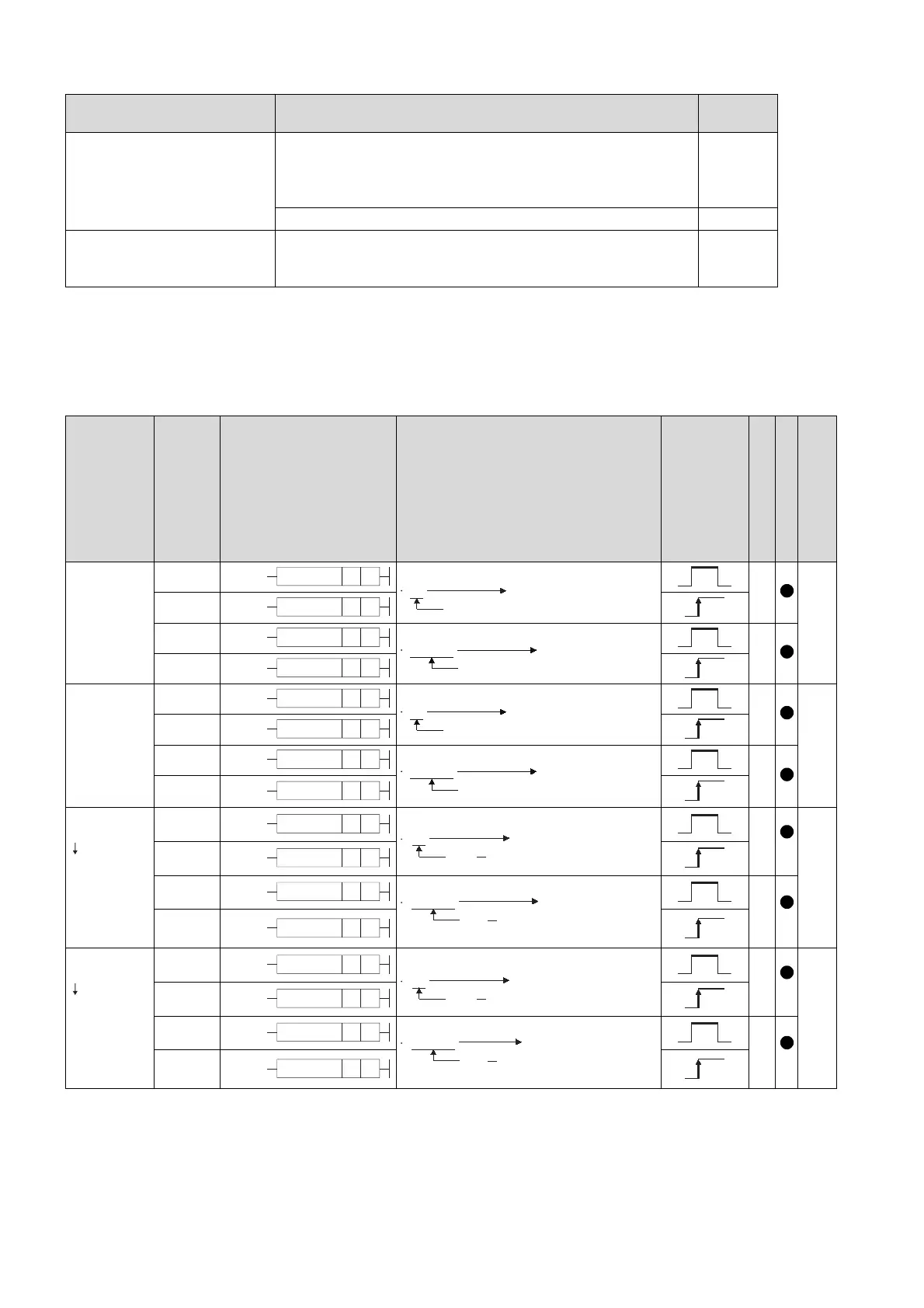

Component Device

Number of

Steps

High Performance model QCPU

Process CPU

Redundant CPU

• Word device: Internal device (except for file register ZR)

• Bit device: Devices whose device Nos. are multiples of 16, whose digit

designation is K8, and which use no indexing.

• Constant: No limitations

3

Note 1)

Devices other than above

2

Note 2)

Basic model QCPU

Universal model QCPU

LCPU

All devices that can be used

2

Note 2)

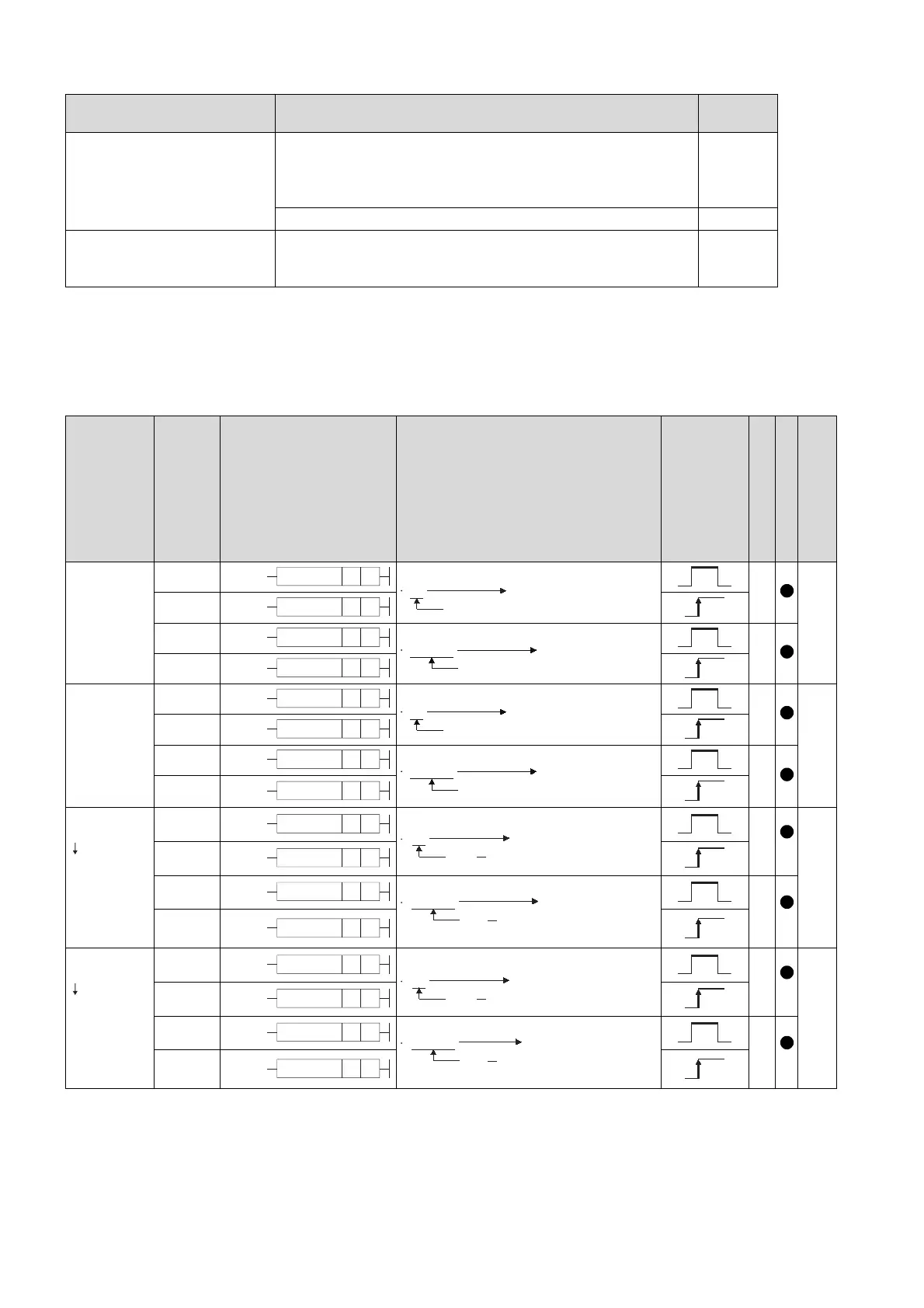

Category

Instruction Symbol

Symbol Processing Details

Execution

Condition

Number of Basic Steps

Subset

See for Description

BCD

conversions

BCD

3

*1

Page

231

BCDP

DBCD

3

*1

DBCDP

BIN

conversions

BIN

3

*1

Page

233

BINP

DBIN

3

*1

DBINP

BIN

Floating point

conversions

(Single

precision)

FLT

3

*1

*2

Page

235

FLTP

DFLT

3

*1

*2

DFLTP

BIN

Floating point

conversions

(Double

precision)

FLTD

4

*2

Page

237

FLTDP

DFLTD

4

*2

DFLTDP

BCD SD

(S) (D)

BIN (0 to 9999)

BCD conversions

BCDP SD

DBCD SD

(S+1, S) (D+1, D)

BIN (0 to 99999999)

BCD conversions

DBCDP SD

BIN SD

(S) (D)

BCD (0 to 9999)

BIN conversions

BINP SD

DBIN SD

(S+1, S) (D+1, D)

BCD (0 to 99999999)

BIN conversions

DBINP SD

FLT SD

(S)

Conversion to real number

(

D+1, D)

BIN(

32768 to 32767)

FLTP SD

DFLT SD

(S+1, S) (D+1, D)

BIN( 2147483648 to

2147483647)

Conversion to real number

DFLTP SD

FLTD S D

(S)

Conversion to real number

(

D+3, D+2, D+1, D)

BIN(

32768 to 32767)

FLTDP S D

DFLTD S D

(S+1, S) (D+3, D+2, D+1, D)

BIN( 2147483648 to

2147483647)

Conversion to real number

DFLTDP S D

Loading...

Loading...