682

FROM, FROMP, DFRO, DFROP

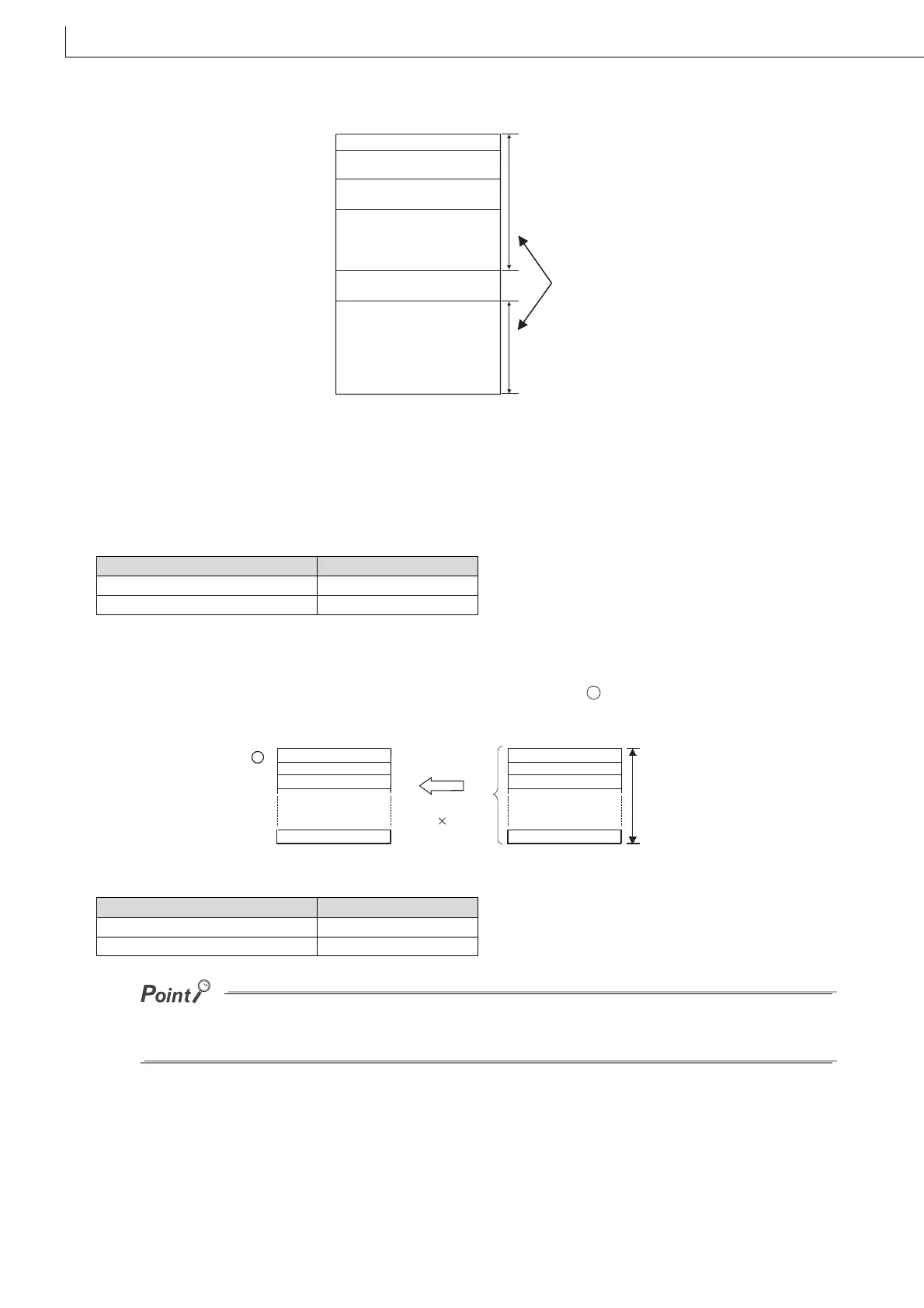

(b) CPU shared memory address of the Universal model QCPU

*3

*2: Usable as a user free area when auto refresh setting is not made.

When auto refresh setting is made, the auto refresh send range and later are usable as a user free area.

*3: With the following CPU modules, data cannot be read from the multiple CPU high speed transmission area.

•Q00UCPU

•Q01UCPU

•Q02UCPU

(2) When 0 is specified in n3 as the number of data to be read, no processing is performed.

(3) The number of data to be read changes depending on the target CPU module.

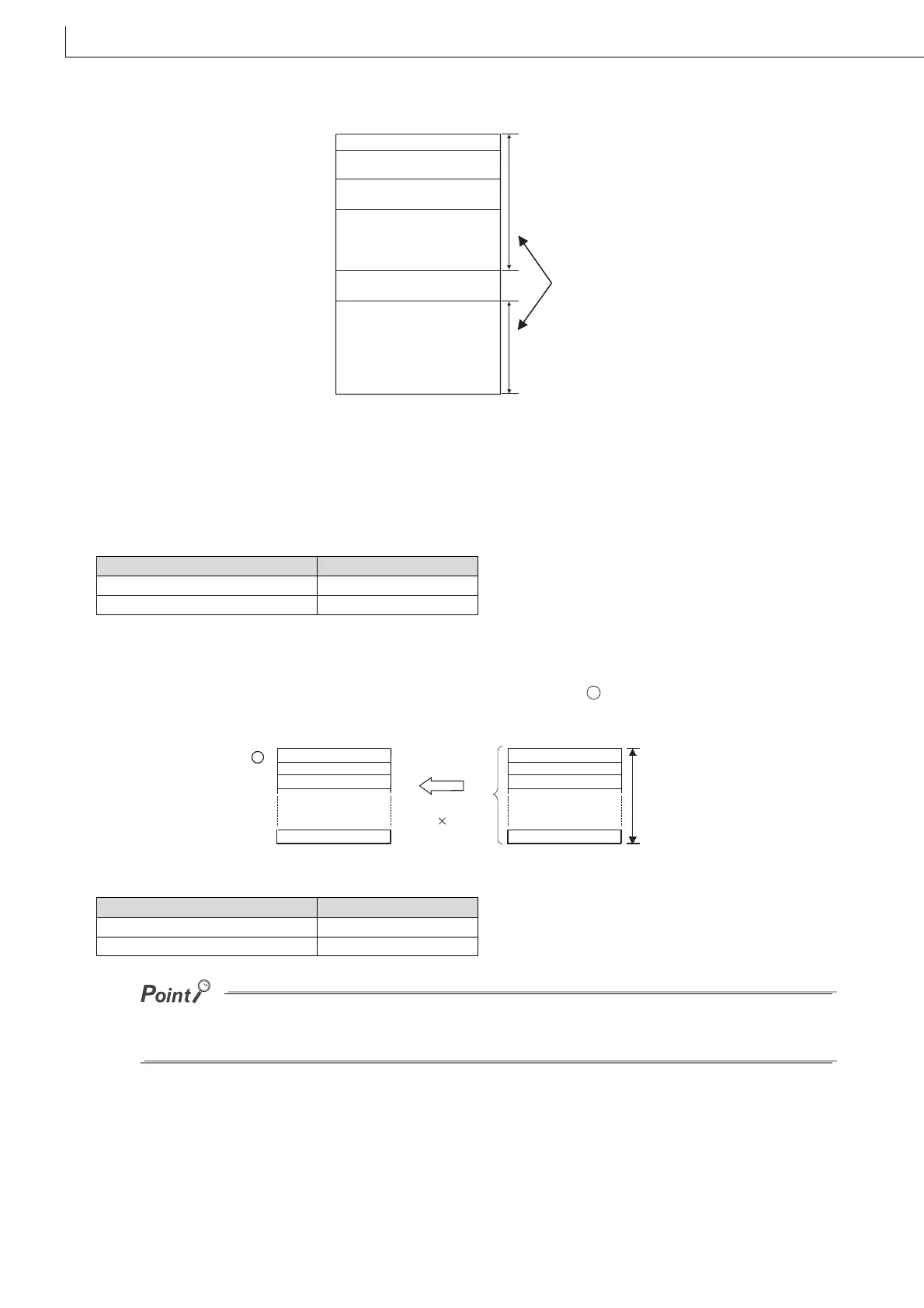

DFRO

(1) Reads the data of (n3×2) words from the CPU shared memory address designated by n2 of the CPU module designated

by n1, and stores that data into the area starting from the device designated by .

(2) When 0 is specified in n3 as the number of data to be read, no processing is performed.

(3) The number of data to be read changes depending on the target CPU module.

Read of data from the CPU shared memory can also be performed using the intelligent function module devices.

For intelligent function module device, refer to the QnUCPU User's Manual (Function Explanation, Program Fundamentals)

or Qn(H)/QnPH/QnPRHCPU User's Manual (Function Explanation, Program Fundamentals).

CPU Module Number of Read Points

Basic model QCPU 1 to 512

Universal model QCPU 1 to 14336

CPU Module Number of Read Points

Basic model QCPU 1 to 256

Universal model QCPU 1 to 7168

Host CPU operation information area

CPU shared memory address

System area

Host CPU refresh area

*2

User free area

Read designation

permitted area

0(0

H)

512(200

H)

2048(800

H)

4096(1000

H)

10000(2710

H)

24335(5F0FH)

Unusable

Multiple CPU high speed

transmisson area

D

n3

CPU shared memory of the

designated CPU (n1)

n

2

Device memory

D

Reads the data

of (n3 2)

words

Loading...

Loading...