739

3

2

3

A

5

6

7

8

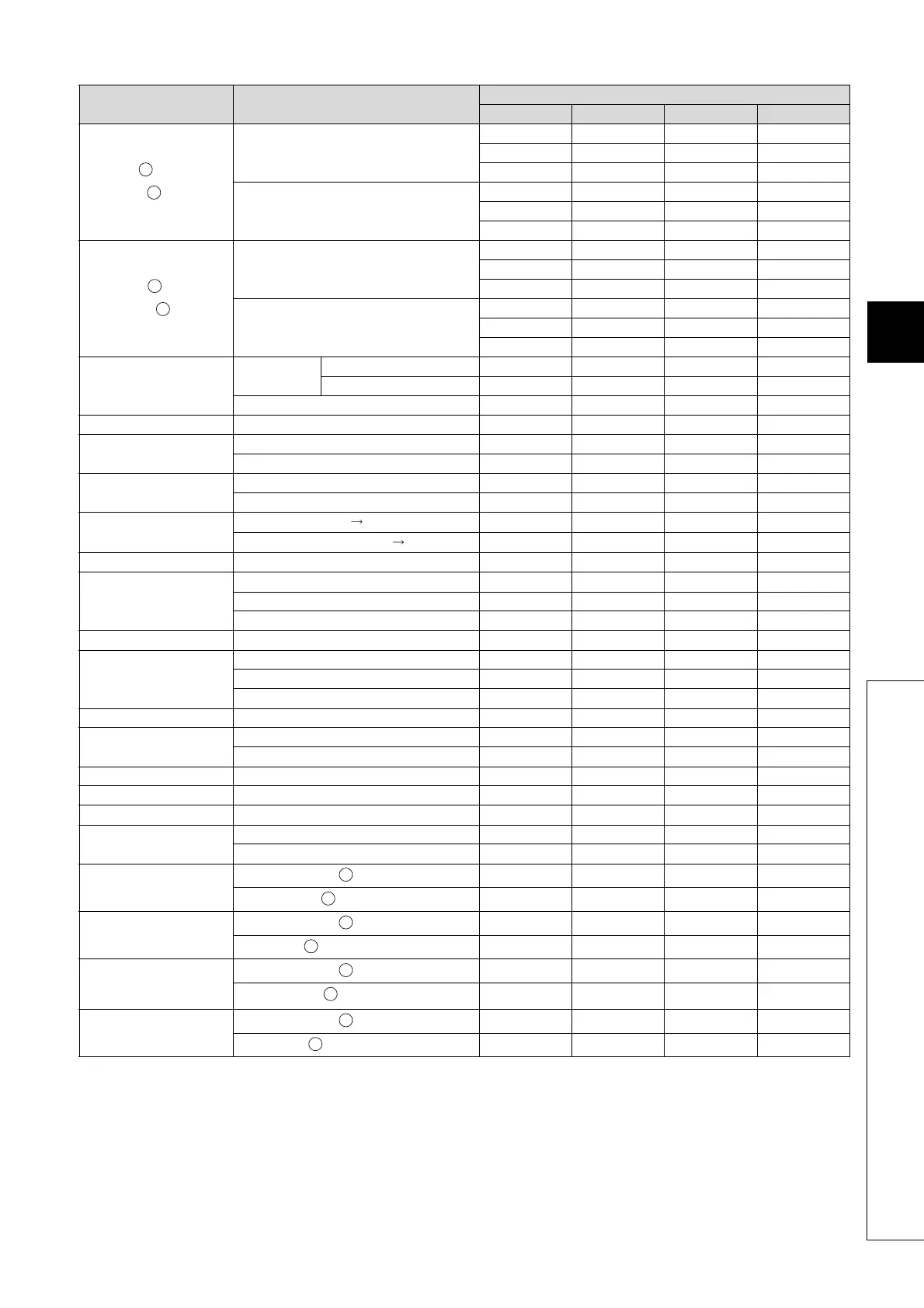

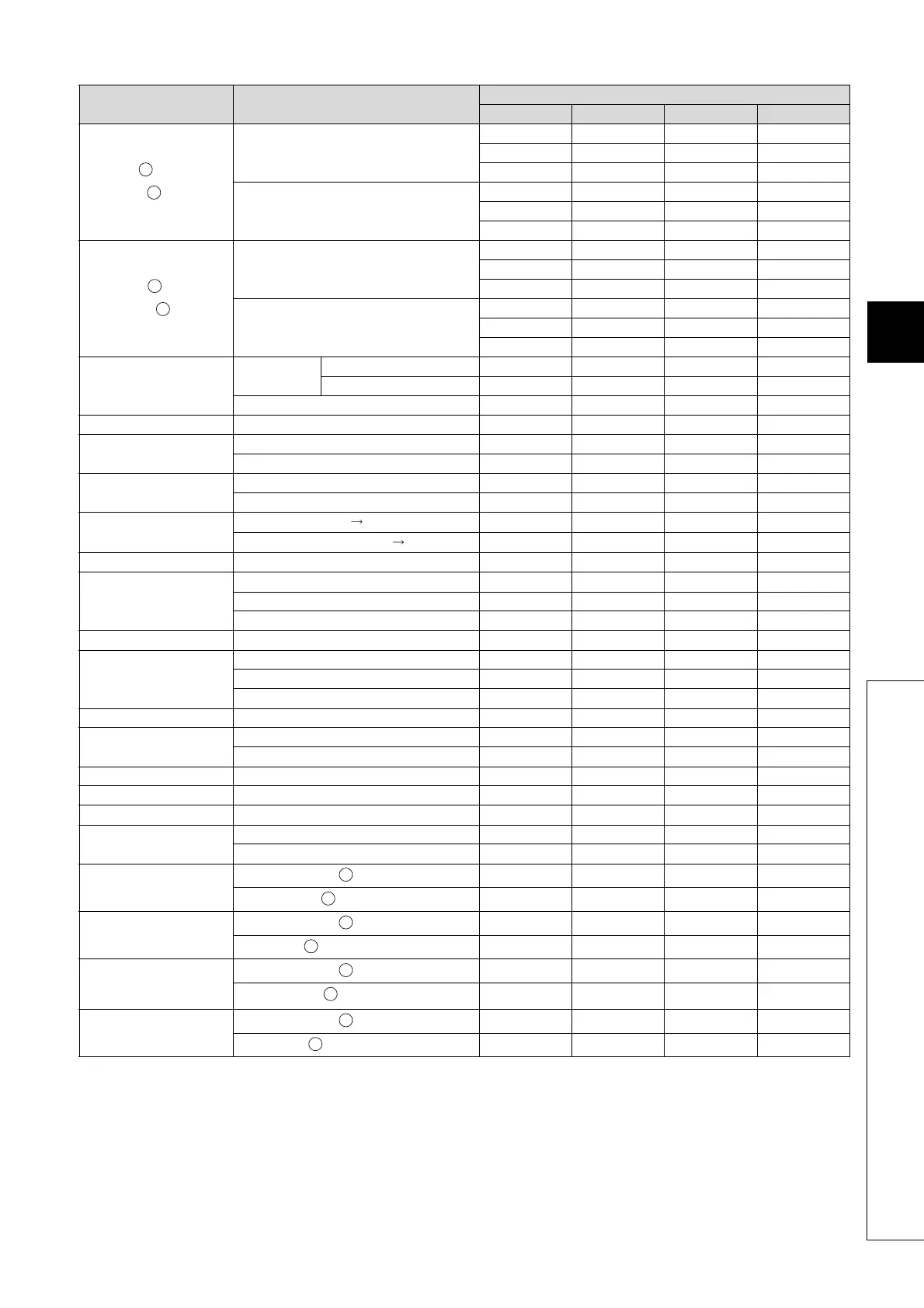

Appendix 1OPERATION PROCESSING TIME

Appendix 1.3Operation Processing Time of High Performance Model QCPU/Process CPU/Redundant

CPU

*1: The upper row indicates the processing time when A38B/A1S38B and the extension base are used.

The center row indicates the processing time when A38HB/A1S38HB is used.

The bottom row indicates the processing times taken when the Q312B is used to execute the instruction for the QJ71C24 in

slot 0.

The FROM/TO instruction differs in processing time according to the number of slots and the loaded modules.

(The QnCPU/QnHCPU also differs in processing time according to the extension base type.)

Instruction Condition (Device)

Processing Time (µs)

Qn QnH QnPH QnPRH

TO n1 n2 n3

TOP n1 n2 n3

*1

n3 = 1

–– –– –– ––

–– –– –– ––

48 20 20 20

n3 = 1000

–– –– –– ––

–– –– –– ––

479 412 412 412

DTO n1 n2 n3

DTOP n1 n2 n3

*1

n3 = 1

–– –– –– ––

–– –– –– ––

50 23 23 23

n3 = 500

–– –– –– ––

–– –– –– ––

457 416 416 416

PR

SM701ON

Variable 1 character 33 11 11 ––

Variable 32 character 48 18 18 ––

SM701OFF 21 7.8 7.8 ––

PRC –– 181 16 16 ––

LED

When displayed ––––––––

Display completed ––––––––

LEDC

When displayed ––––––––

Display completed ––––––––

LEDR

No display no display

0.40 0.17 0.17 0.17

LED instruction execution no display

103444444

CHKST –– 5.8 2.5 2.5 2.5

CHK

1 contact no error 24 10 10 10

150 contact no error 1676 721 721 721

1 contact error 88 38 38 38

CHKCIR 10 steps 5.8 2.5 2.5 2.5

SLT

All internal devices ––––––––

File register 8k points –– –– –– ––

SLT execution completion –– –– –– ––

SLTR –– –– –– –– ––

STRA

Start ––––––––

STRA execution completion –– –– –– ––

STRAR –– ––––––––

PTRA –– –– –– –– ––

PTRAR –– ––––––––

PTRAEXE

PTRAEXEP

When operating –– –– –– ––

Trace in progress –– –– –– ––

BINDA

BINDAP

= 1

15 6.7 6.7 6.7

= - 32768

24 10 10 10

DBINDA

DBINDAP

= 1

43 18 18 18

= - 2147483648

86 37 37 37

BINHA

BINHAP

= 1

18 7.7 7.7 7.7

= FFFF

H

19 8.2 8.2 8.2

DBINHA

DBINHAP

= 1

23 10 10 10

= FFFFFFFF

H

24 10 10 10

S

S

S

S

S

S

S

S

S

S

S

S

Loading...

Loading...