App - 100

APPENDICES

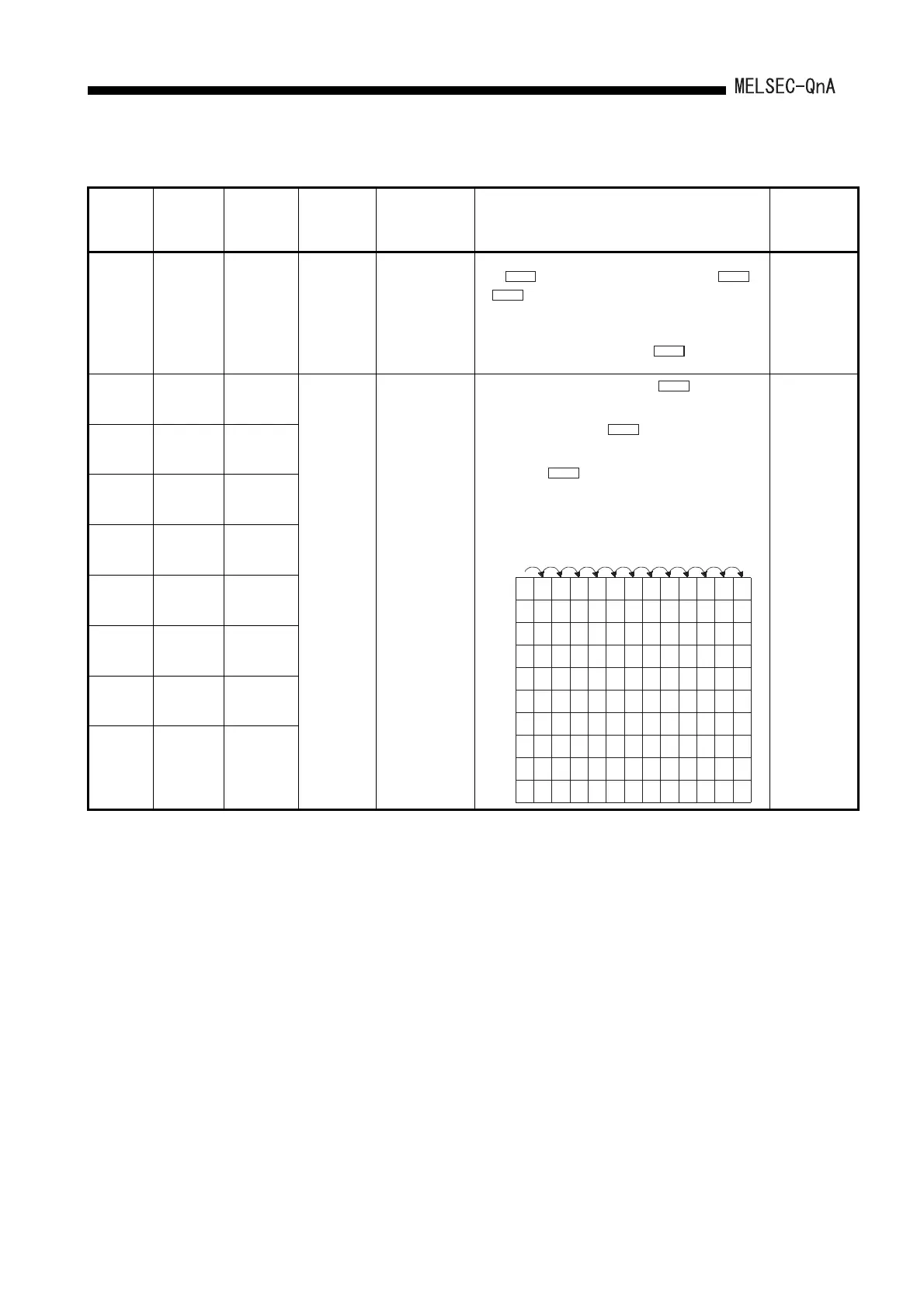

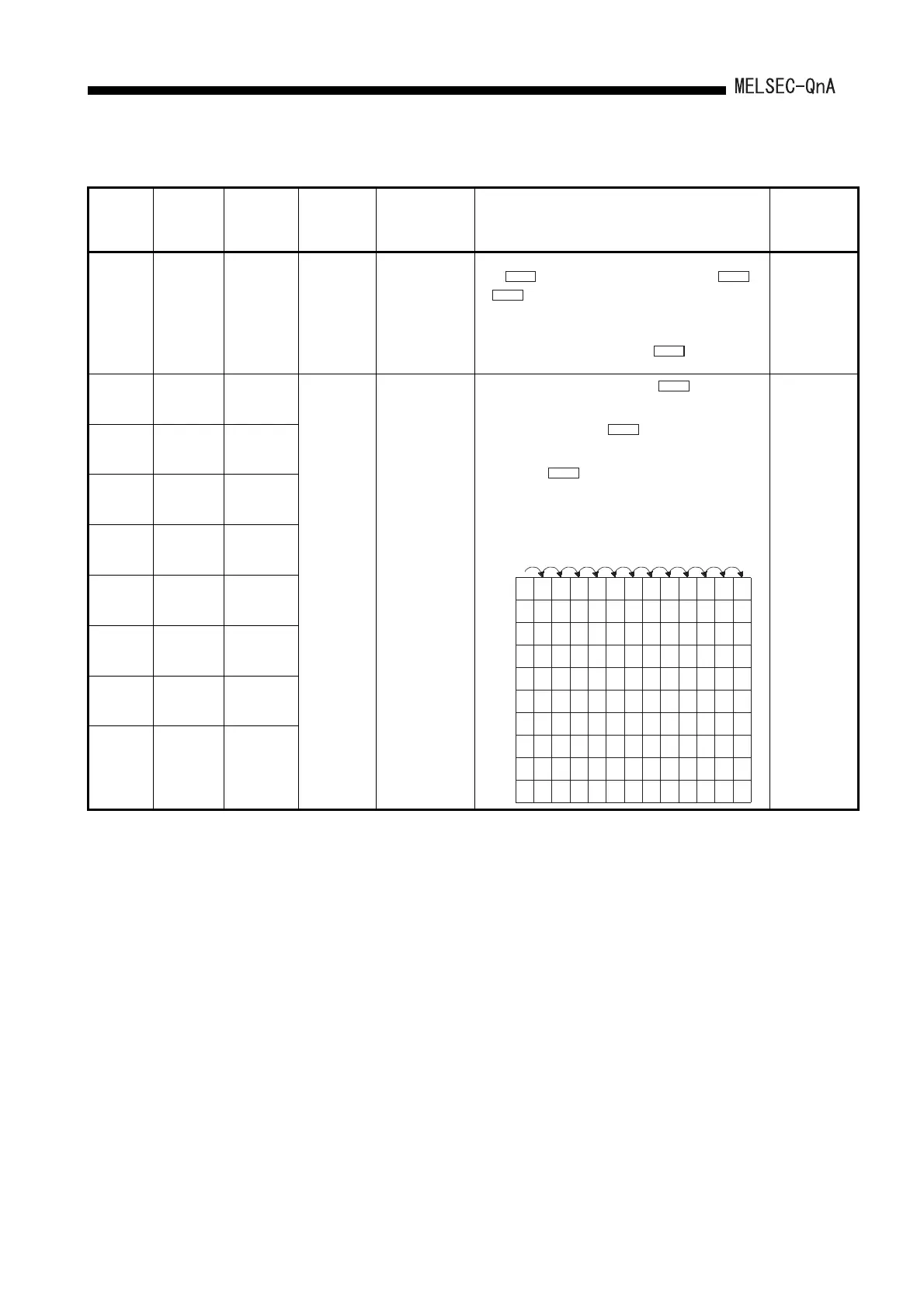

Table App. 3.11. Special register

ACPU

Special

Register

Special

Register

after

Conversion

Special

Register for

Modification

Name Meaning Details

Corresponding

CPU

D9124 SD1124 SD63

Number of

annuciator

detections

Number of annuciator

detections

• When one of F0 to 255 (F0 to 2047 for AuA and AnU) is turned on

by 1 is added to the contents of SD63. When or

instruction is executed, 1 is subtracted from the contents

of SD63.

(If the INDICATOR RESET switch is provided to the CPU module,

pressing the switch can execute the same processing.)

• Quantity, which has been turned on by is stored into

SD63 in BIN code. The value of SD63 is maximum 8.

QnA

D9125 SD1125 SD64

Annunciator

detection

number

Annunciator detection

number

• When any of F0 to 2047 is turned on by , the annunciator

numbers (F numbers) that are turned on in order are registered into

D9125 to D9132.

• The F number turned off by is erased from any of D9125

to D9132, and the F numbers stored after the erased F number are

shifted to the preceding registerers.

By executing instruction, the contents of SD64 to SD71

are shifted upward by one. (For A3N, A3HCPU, it can be

performed by use of INDICATOR RESET switch on front of CPU

module.)

When there are 8 annunciator detections, the 9th one is not stored

into SD64 to SD71 even if detected.

QnA

D9126 SD1126 SD65

D9127 SD1127 SD66

D9128 SD1128 SD67

D9129 SD1129 SD68

D9130 SD1130 SD69

D9131 SD1131 SD70

D9132 SD1132 SD71

SET F RST F

LEDR

SET F

SET F

RST F

LEDR

0 505050505050505050505099

0

0 5050505050505050505099

025

25 99 99 99 99 99 99 99 99 15

123234567888

50

0

0 99 1515151515151570

00 0

0 70707070707065

00 000

0 656565656538

00 0000

0 38383838

110

00 0000

0

0 110 110 110

151

00 0000

0

0

151 151 210

00 0000

0

0

00

SD62

SD63

SD64

SD65

SD66

SD67

SD68

SD69

SD70

SD71

SET

F50

SET

F25

SET

F99

RST

F25

SET

F15

SET

F70

SET

F65

SET

F38

SET

F110

SET

F151

SET

F210

LEDR

Loading...

Loading...