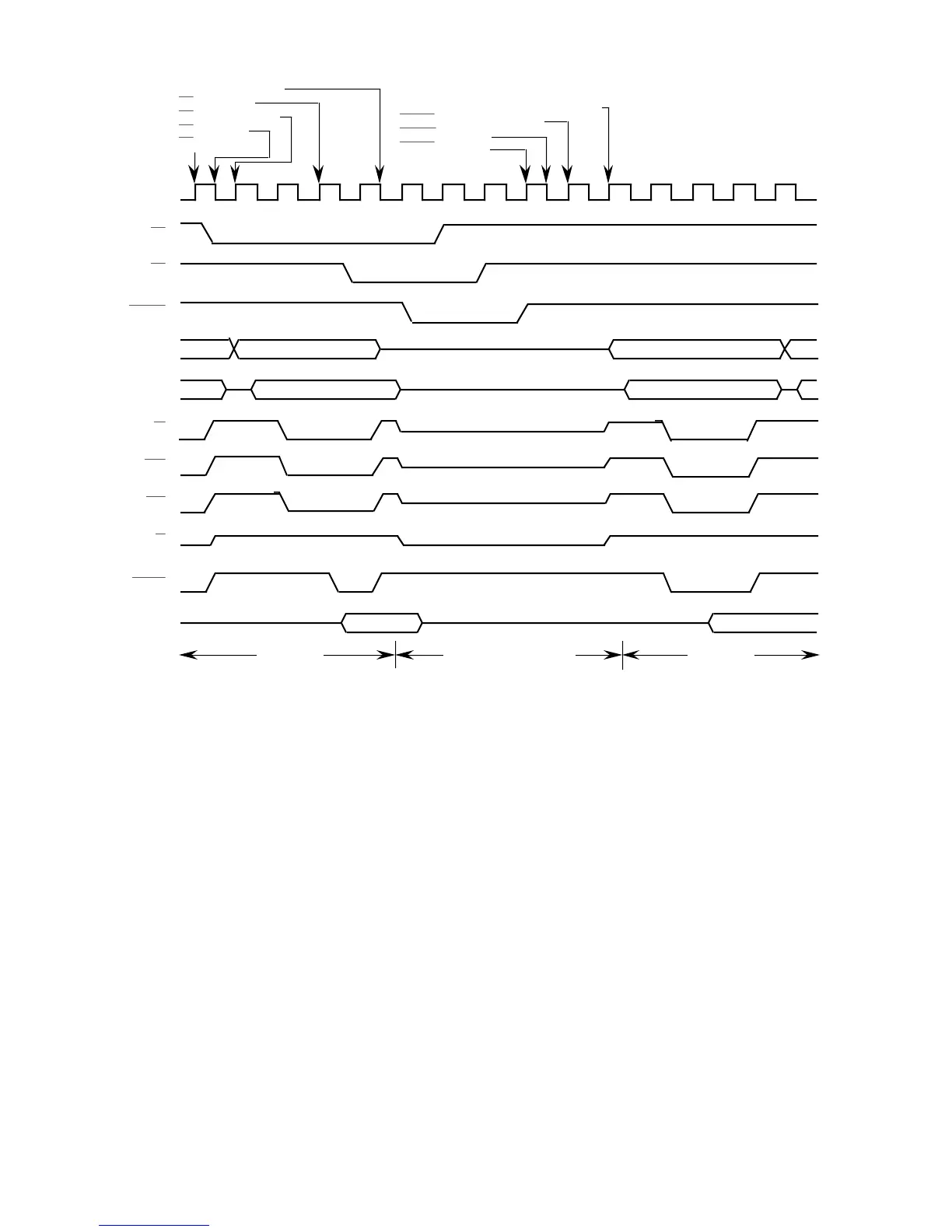

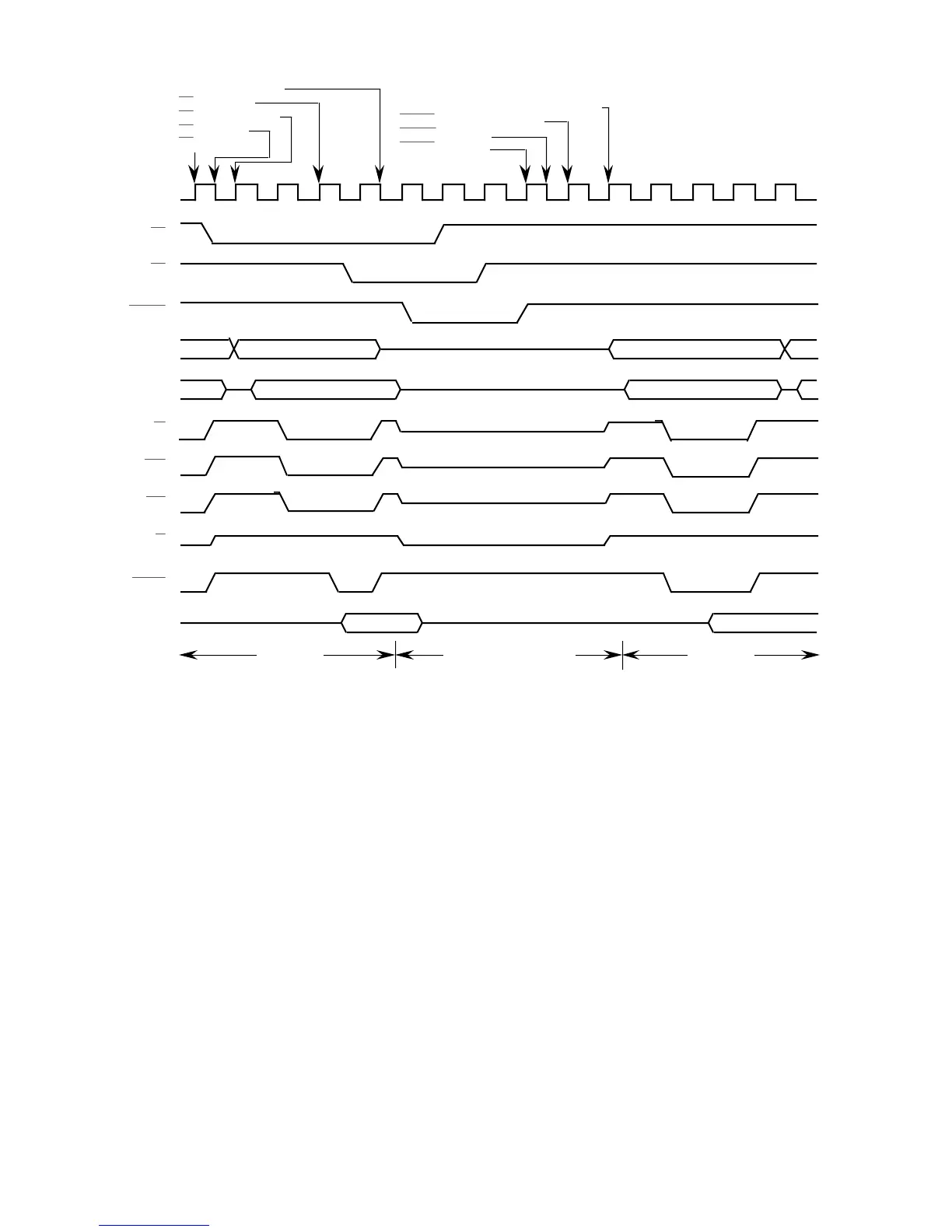

5- 20 M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL MOTOROLA

G ASSERTED

R VALID INTERNA

R SAMPLED

R ASSERTED

BUS RELEASED FROM THREE STATE AND

P

ROCESSOR STARTS NEXT BUS CYCLE

GACK NEGATED INTERNAL

GACK SAMPLED

GACK NEGATED

Figure 5-21. 3-Wire Bus Arbitration Timing Diagram—Special Case

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...