Table 34. LVTTL Lines (Continued)

GPIC Signal Onboard Function Direction (to

GPIC)

Active State Disconnecting

Resistor

DIO28 MUX A0 (TC Input) Output Low/High R135

DIO29 DS3 (Green LED) Output Low R136

DIO30 DS2 (Green LED) Output Low R143

DIO31 DS1 (Red LED) Output Low R151

The sbRIO-9683 LVTTL DIO lines connect directly to the FPGA DIO on the

sbRIO-9505/9506/9507 and are unbuffered and unprotected.

Caution Operating the LVTTL DIO outside the rated specifications may result in

permanent damage to the FPGA on the sbRIO-9605/9606/9607.

If overshoot, undershoot, and signal integrity are concerns for your application, use a single

load per line that does not exceed 25 pF.

The LVTTL DIO channels on the sbRIO-9687 are routed with a 50 Ω impedance trace. It is

recommended to route all external circuitry with a similar impedance to ensure the best signal

quality.

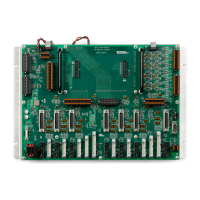

Expansion Board

LVTTL lines are available at two expansion connectors that allow a custom expansion board

to be placed on top of the sbRIO-9687 interface board.

Expansion Board Connectors

Each expansion board connector (J7 and J8) consists of a 26-pin header. For information about

mating connectors, refer to the Connectors on page 4 section. The following tables provide

pinout information for the expansion board connectors.

Table 35. LVTTL Expansion Connector Pinout (J7)

Pin Signal Pin Signal

Loading...

Loading...