LTE-A Module Series

EP06 Series Hardware Design

EP06_Series_Hardware_Design 24 / 56

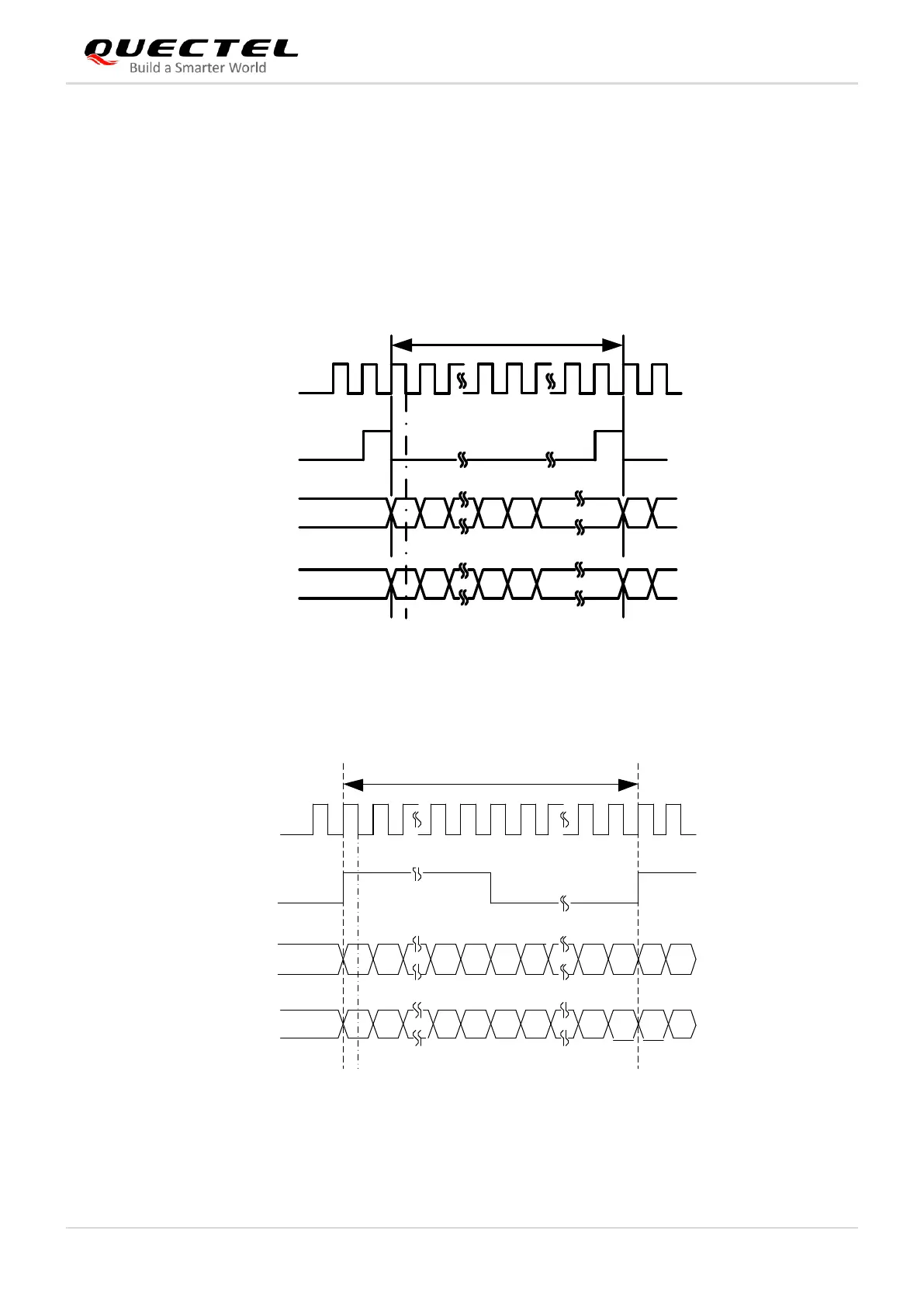

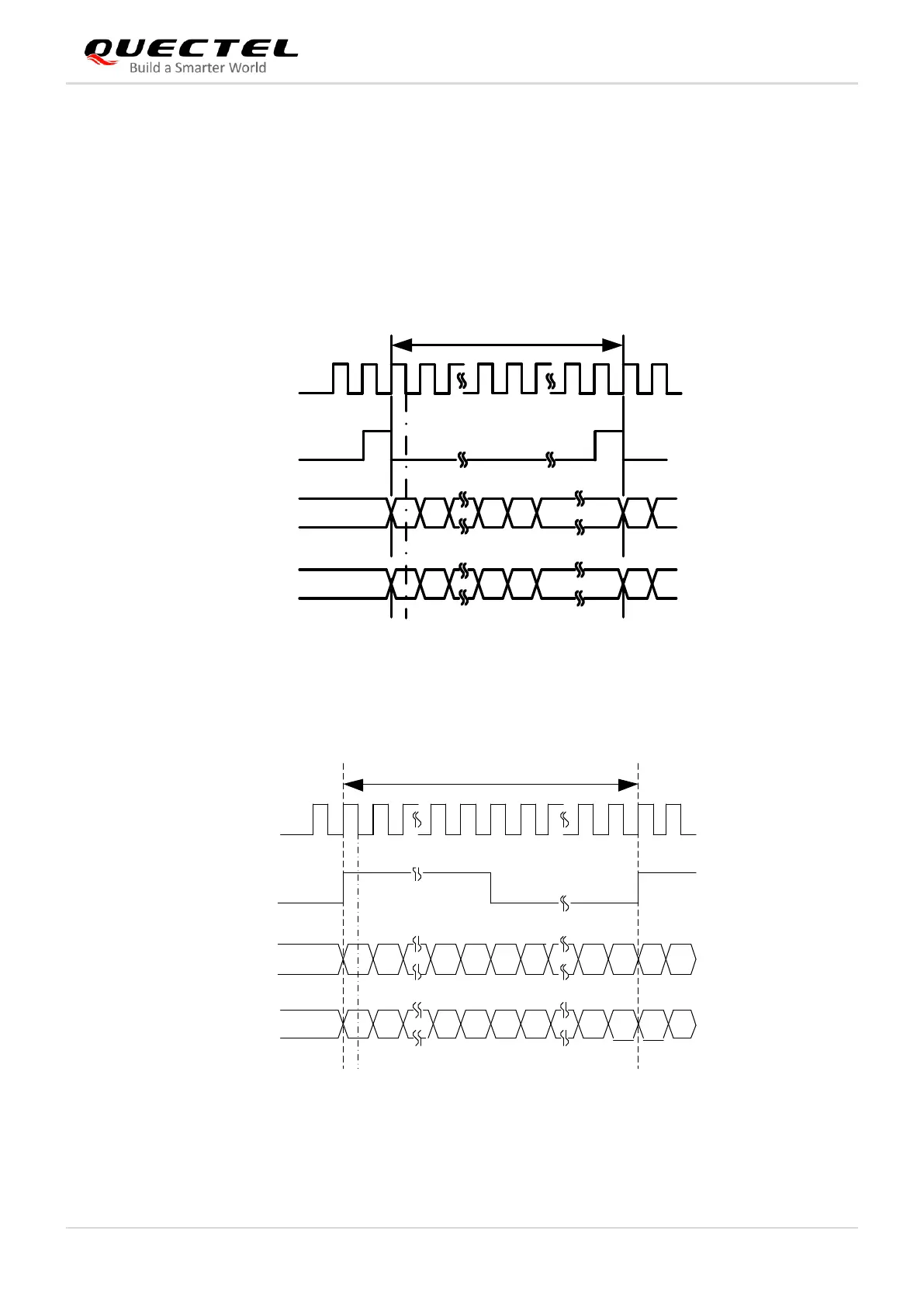

In auxiliary mode, the data is sampled on the falling edge of the PCM_CLK and transmitted on the rising

edge. The PCM_SYNC rising edge represents the MSB. In this mode, PCM interface operates with a 256

kHz PCM_CLK and an 8 kHz, 50% duty cycle PCM_SYNC only.

The module supports 16-bit linear data format. The following figures show the primary mode’s timing

relationship with 8 kHz PCM_SYNC and 2048 kHz PCM_CLK, as well as the auxiliary mode’s timing

relationship with 8 kHz PCM_SYNC and 256 kHz PCM_CLK.

PCM_CLK

PCM_SYNC

PCM_DOUT

MSB

LSB

MSB

125 µs

1 2 256255

PCM_DIN

MSB

LSBMSB

Figure 6: Primary Mode Timing

PCM_CLK

PCM_SYNC

PCM_DOUT

MSB

LSB

PCM_DIN

125us

MSB

1 2 3231

LSB

Figure 7: Auxiliary Mode Timing

Loading...

Loading...