AR-M207 M165 M162 ELECTRICAL SECTION 13-2

2. Circuit descriptions

A. Main PWB (MCU)

(1) General

The MCU PWB is composed of:

• CPU peripheral sections which perform mechanical sequence control

and function job management

• Image process ASIC which performs image process, CCD control, LSU

control, and print control

• Motor control circuit

• Mechanical load, sensor I/O circuit

It controls the processes for copying, the transport loads, fusing, the

optical system, the operation panel, and the option PWB.

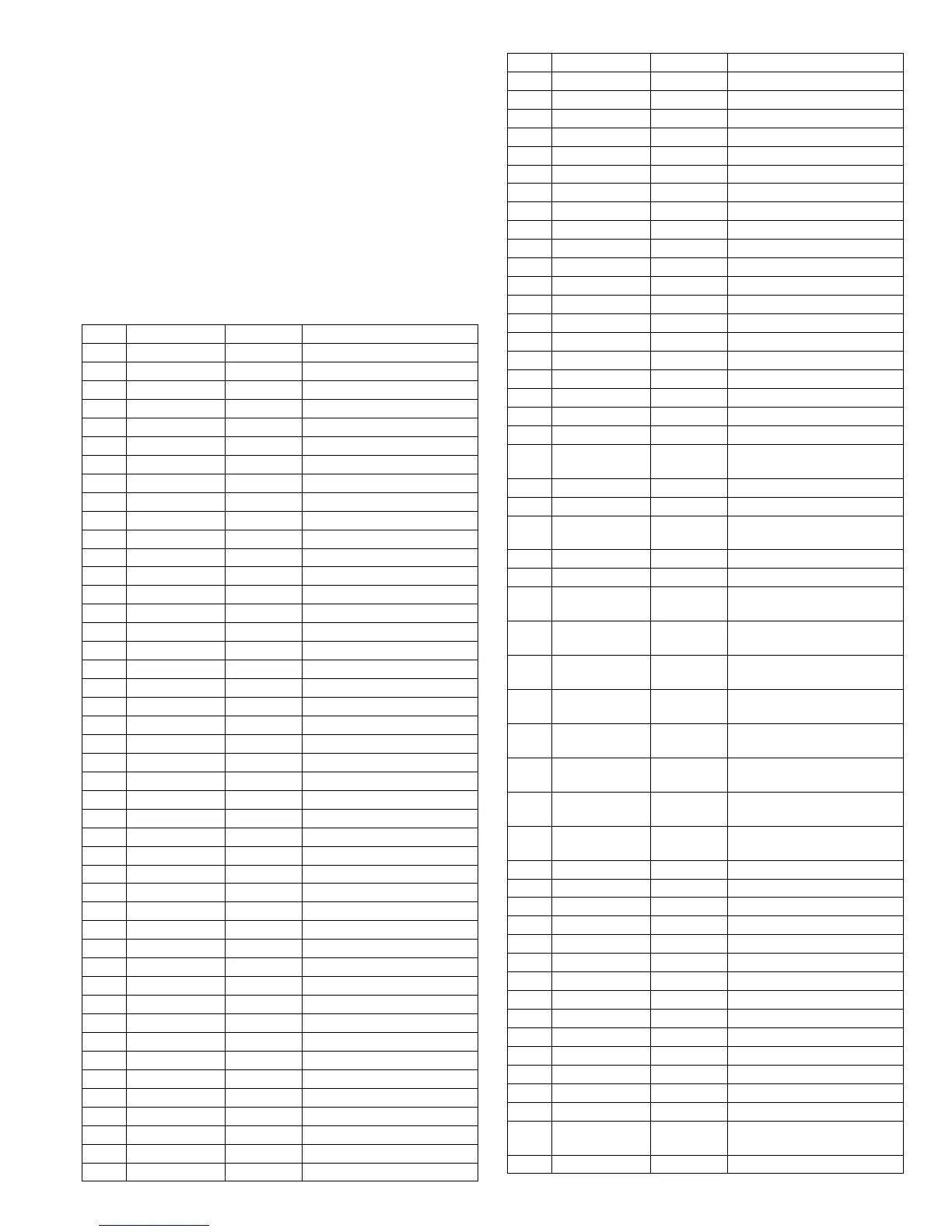

(2) CPU signal table (H8S/2321)

No. SIGNAL In/Out DESCRIPTION

1 PG3/CS1 Out ChipSelect for SRAM

2 PG4/CS0 Out ChipSelect for ROM

3 Vss GND Ground

4 NC GND Ground

5 Vcc 3.3V Power

6 PC0/A0 Pull-Up Address Bus

7 PC1/A1 Out Address Bus

8 PC2/A2 Out Address Bus

9 PC3/A3 Out Address Bus

10 Vss GND Ground

11 PC4/A4 Out Address Bus

12 PC5/A5 Out Address Bus

13 PC6/A6 Out Address Bus

14 PC7/A7 Out Address Bus

15 PB0/A8 Out Address Bus

16 PB1/A9 Out Address Bus

17 PB2/A10 Out Address Bus

18 PB3/A11 Out Address Bus

19 Vss GND Ground

20 PB4/A12 Out Address Bus

21 PB5/A13 Out Address Bus

22 PB6/A14 Out Address Bus

23 PB7/A15 Out Address Bus

24 PA0/A16 Out Address Bus

25 PA1/A17 Out Address Bus

26 PA2/A18 Out Address Bus

27 PA3/A19 Out Address Bus

28 Vss GND Ground

29 PA4/A20/IRQ4 Pull-Up Address Bus

30 PA5/A21/IRQ5 In EXT-PCB Wake Up Interrupt

31 PA6/A22/IRQ6 In SPF Paper Detect Interrupt

32 PA7/A23/IRQ7 In ASIC Interrupt

33 P67/IRQ3/CS7 In Mirror Home Position Interrupt

34 P66/IRQ2/CS6 In ASIC Interrupt

35 Vss GND Ground

36 Vss GND Ground

37 P65/IRQ1 In Zero Cross Interrupt

38 P64/IRQ0 In ASIC Interrupt

39 Vcc 3.3V Power

40 PE0/D0 In/Out Data Bus

41 PE1/D1 In/Out Data Bus

42 PE2/D2 In/Out Data Bus

43 PE3/D3 In/Out Data Bus

44 Vss GND Ground

45 PE4/D4 In/Out Data Bus

46 PE5/D5 In/Out Data Bus

47 PE6/D6 In/Out Data Bus

48 PE7/D7 In/Out Data Bus

49 PD0/D8 In/Out Data Bus

50 PD1/D9 In/Out Data Bus

51 PD2/D10 In/Out Data Bus

52 PD3/D11 In/Out Data Bus

53 Vss GND Ground

54 PD4/D12 In/Out Data Bus

55 PD5/D13 In/Out Data Bus

56 PD6/D14 In/Out Data Bus

57 PD7/D15 In/Out Data Bus

58 Vcc 3.3V Power

59 P30/TxD0 Out CRUM I2C Bus Control

60 P31/TxD1 Out For Debug

61 P32/RxD0 In/Out 12C Bus DATA

62 P33/RxD1 Option Cassette Detect Signal

63 P34/SCK0 Out 12C Bus Clock

64 P35/SCK1 In USB Detect Signal

65 Vss GND Ground

66 P60/DREQ0/

CS4

Out Not use

67 Vss GND Ground

68 Vss GND Ground

69 P61/TEND0/

CS5

In Flash ROM Ready/Busy

70 P62/DREQ1 Out Outconnect telephone control

71 P63/TEND1 Out USB I/F Control

72 P27/PO7/

TIOCB5/TMO1

Out Not use

73 P26/PO6/

TIOCA5/TMO0

Out

74 P25/PO5/

TIOCB4/TMCI1

Out Power OFF Signal

75 P24/PO4/

TIOCA4/TMRI1

Print Start Signal

76 P23/PO3/

TIOCD3/TMRI0

Out Duplex Motor Drive

77 P22/PO2/

TIOCC3/TMRI0

Out Duplex Motor Drive

78 P21/PO1/

TIOCB3

Out Duplex Motor Drive

79 P20/PO0/

TIOCA3

Out Duplex Motor Drive

80 WDTOVF Pull-Up Watchdog Timer Over flow

81 RES In Reset Input

82 NMI Pull-Up NMI Interrupt

83 STBY Pull-Up Stand-by

84 Vcc 3.3V Power

85 XTAL 19.6608MHz System Clock

86 EXTAL 19.6608MHz System Clock

87 Vss GND Ground

88 PF7/fai Pull-Up System Clock

89 Vcc 3.3V Power

90 RF6/AS Out Software Reset Signal

91 RD Out Read Enable

92 HWR Out High Write Enable

93 PF3/LWR Out Low Write Enable

94 PF2/LCAS/

WAIT/BREQO

Out 151 Selector Signal

95 PF1/BACK Out 151 Selector Signal

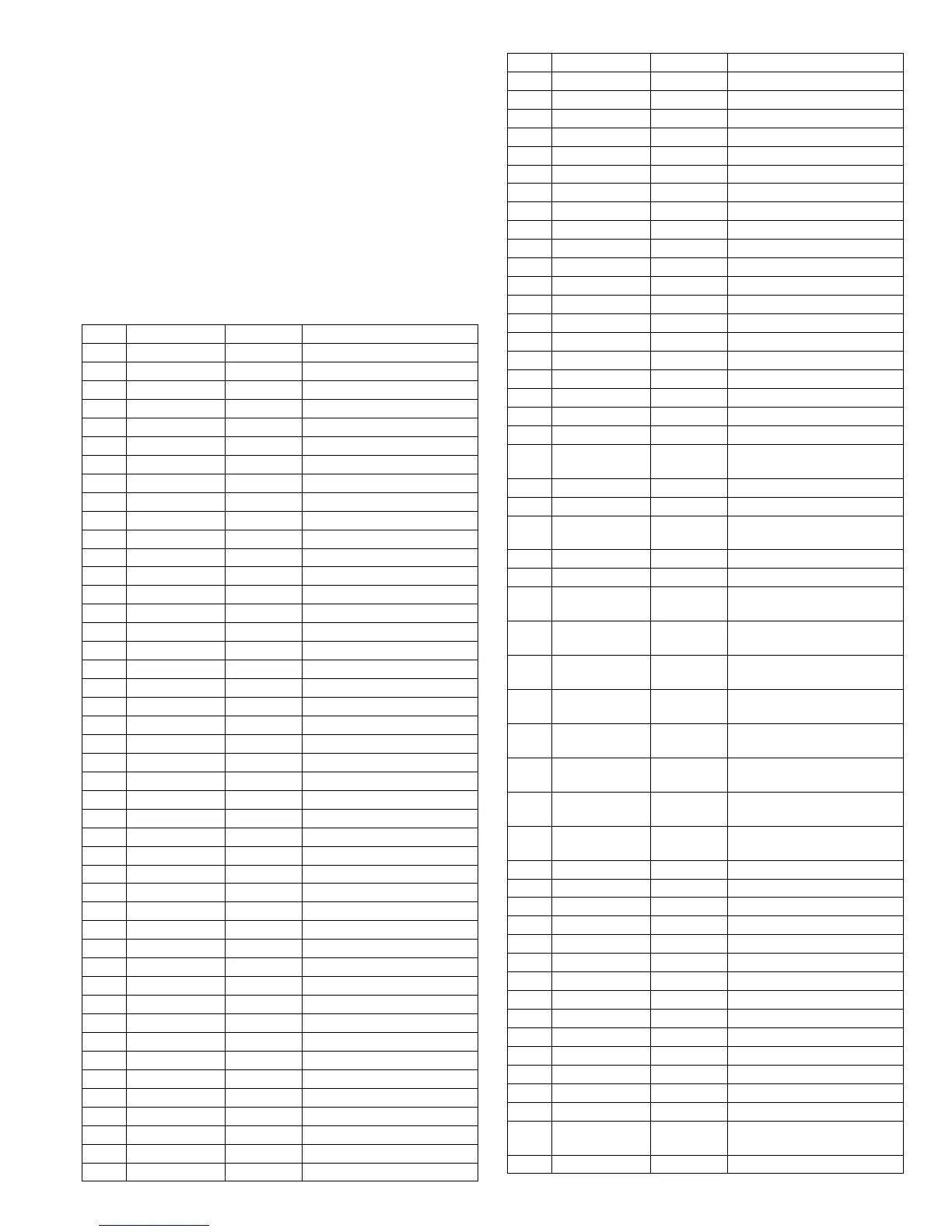

No. SIGNAL In/Out DESCRIPTION

[13]ELECTRICALSECTION.fm 2 ページ 2004年11月12日 金曜日 午後2時21分

Loading...

Loading...