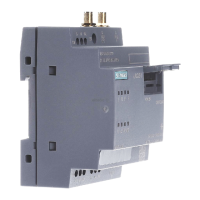

CPU modules

4.1 CPU module CPU555

SIMATIC TDC hardware

System Manual, 08/2017, A5E01114865-AL

85

2 GB DDR3-1333 MHz (667 MHz)

Caches

• L1 cache: 32 KB data + 32 KB instruction

• L2 cache: 256 KB data/instruction

• L3 cache: 3 MB

256 MB DDR2-400 (150 MHz)

Cache

• L1 cache: 32 KB data + 32 KB instruction

Shared communication memory

Number 3

Allocation of the slots

• Program memory S7 MMC (X4)

• PMC-/XMC plug-in cards (X5)

1)

1)

PMC/XMC plug-in cards are currently not provided.

Fast CPU-CPU communication

CPU555 supports P0 functionality.

Each CPU555 can communicate with up to 7 additional CPU555 by means of the PCIe

interface via the backplane bus (P0 connector). This means that a point-to-point connection

always exists between any two CPU555 modules (see Areas of application (Page 39)).

The user program executed on the CPU module is configured on a PC using STEP 7 /

HW Config and CFC and then downloaded to program memory.

The program memory must be located in the CPU module slot provided (X4).

Direct user program download from the PC to program memory in the CPU module via

PROFINET interface (online loading).