SN8P2501D

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 54 Version 1.5

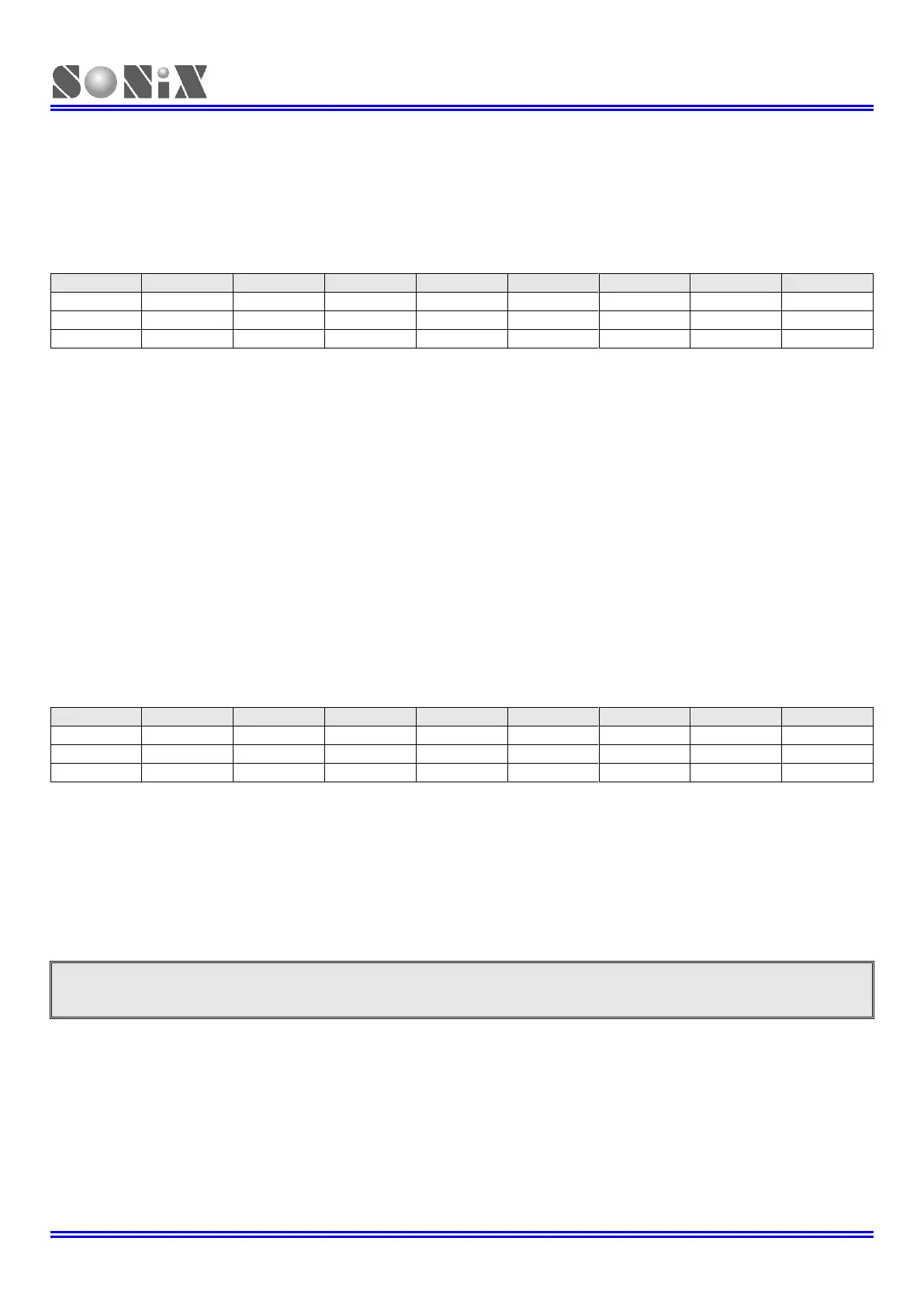

6.3 INTRQ INTERRUPT REQUEST REGISTER

INTRQ is the interrupt request flag register. The register includes all interrupt request indication flags. Each one of the

interrupt requests occurs, the bit of the INTRQ register would be set “1”. The INTRQ value needs to be clear by

programming after detecting the flag. In the interrupt vector of program, users know the any interrupt requests

occurring by the register and do the routine corresponding of the interrupt request.

Bit 0 P00IRQ: External P0.0 interrupt (INT0) request flag.

0 = None INT0 interrupt request.

1 = INT0 interrupt request.

Bit 4 T0IRQ: T0 timer interrupt request flag.

0 = None T0 interrupt request.

1 = T0 interrupt request.

Bit 5 TC0IRQ: TC0 timer interrupt request flag.

0 = None TC0 interrupt request.

1 = TC0 interrupt request.

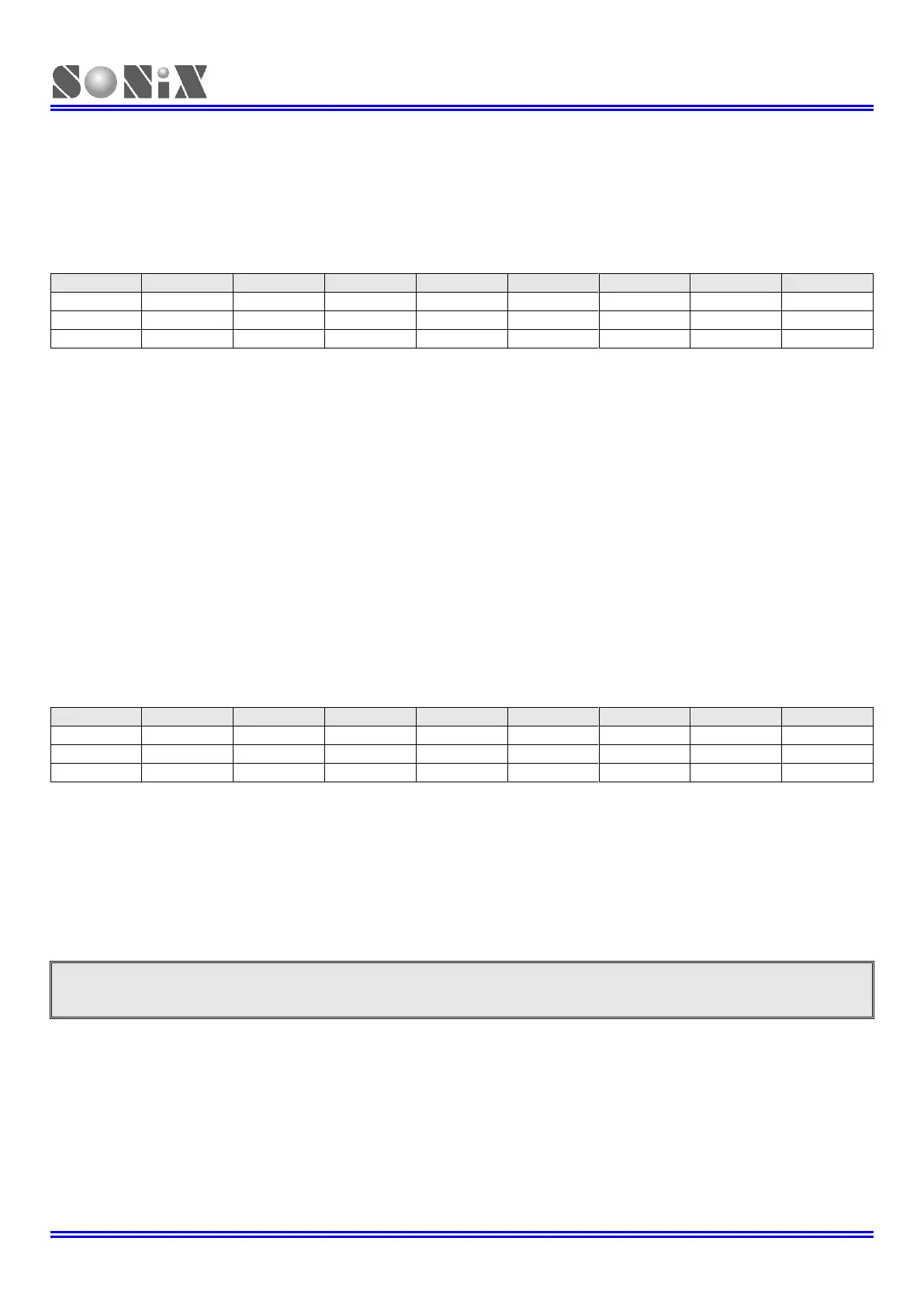

6.4 GIE GLOBAL INTERRUPT OPERATION

GIE is the global interrupt control bit. All interrupts start work after the GIE = 1 It is necessary for interrupt service

request. One of the interrupt requests occurs, and the program counter (PC) points to the interrupt vector (ORG 8) and

the stack add 1 level.

Bit 7 GIE: Global interrupt control bit.

0 = Disable global interrupt.

1 = Enable global interrupt.

Example: Set global interrupt control bit (GIE).

Note: The GIE bit must enable during all interrupt operation.

Loading...

Loading...