SN8P2501D

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 82 Version 1.5

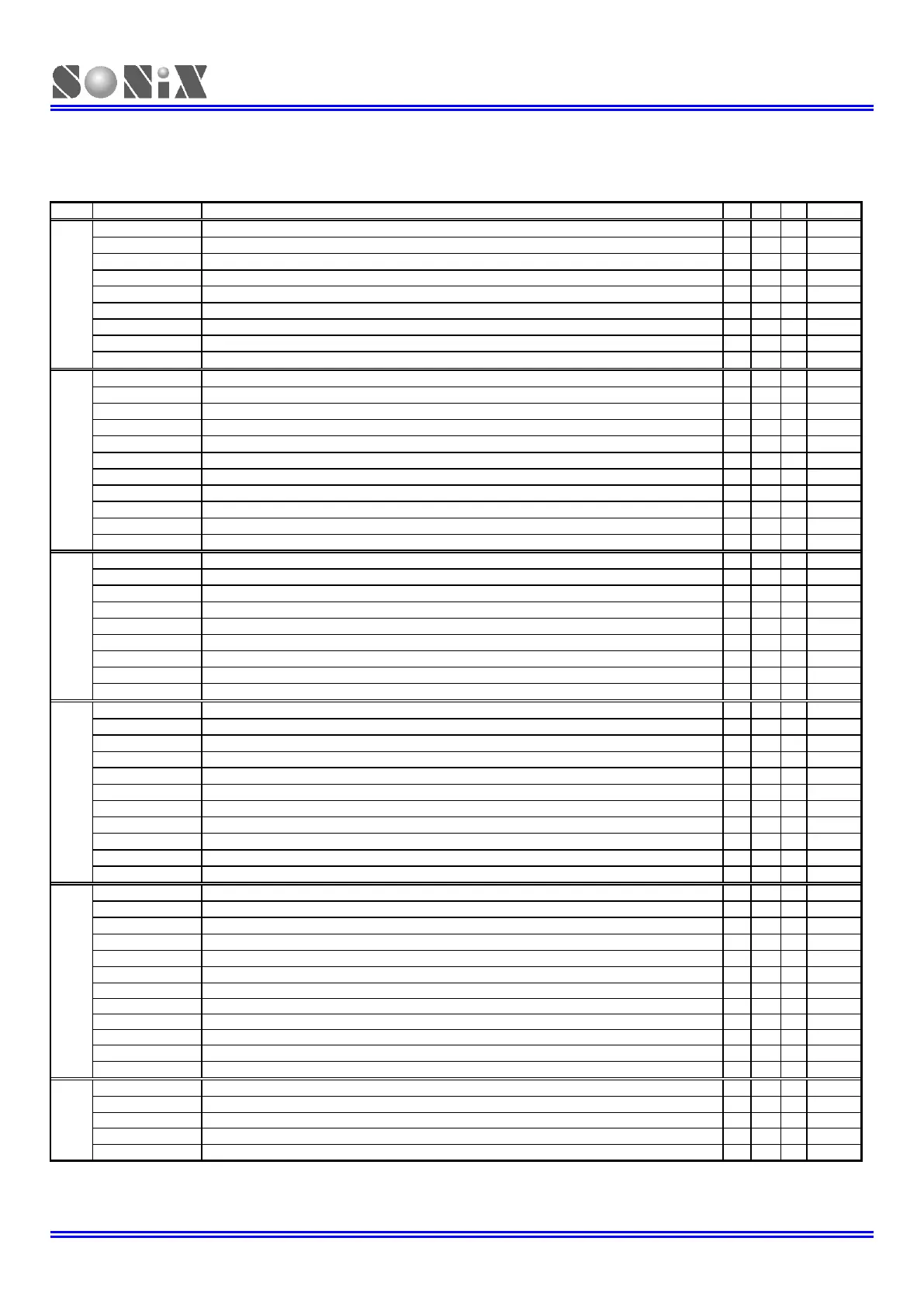

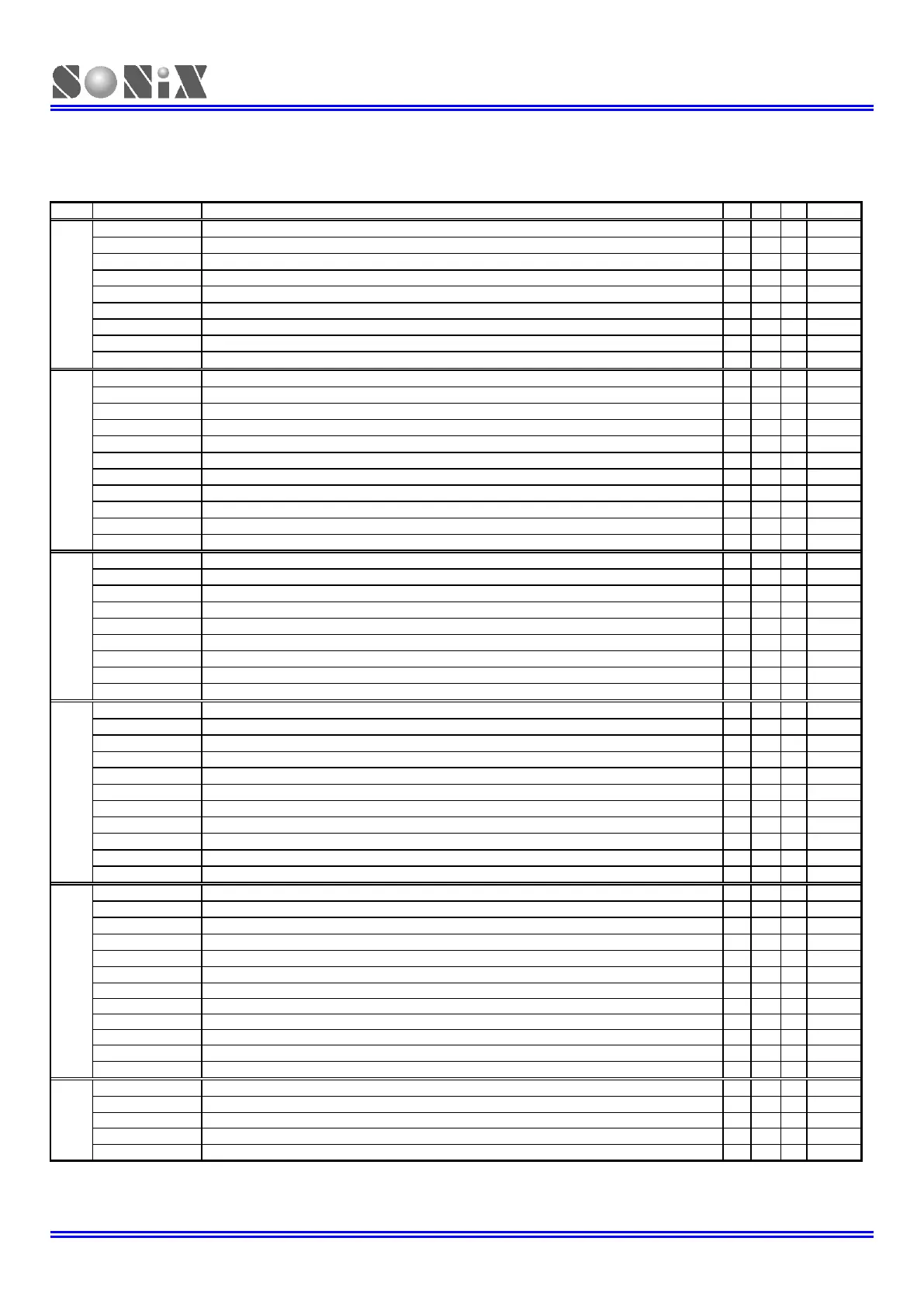

INSTRUCTION TABLE

M I, “M” only supports 0x80~0x87 registers (e.g. PFLAG,R,Y,Z…).

A A + M + C, if occur carry, then C=1, else C=0

M A + M + C, if occur carry, then C=1, else C=0

A A + M, if occur carry, then C=1, else C=0

M A + M, if occur carry, then C=1, else C=0

M (bank 0) M (bank 0) + A, if occur carry, then C=1, else C=0

A A + I, if occur carry, then C=1, else C=0

A A - M - /C, if occur borrow, then C=0, else C=1

M A - M - /C, if occur borrow, then C=0, else C=1

A A - M, if occur borrow, then C=0, else C=1

M A - M, if occur borrow, then C=0, else C=1

A A - I, if occur borrow, then C=0, else C=1

A (b3~b0, b7~b4) M(b7~b4, b3~b0)

M(b3~b0, b7~b4) M(b7~b4, b3~b0)

ZF,C A - I, If A = I, then skip next instruction

ZF,C A – M, If A = M, then skip next instruction

A M + 1, If A = 0, then skip next instruction

M M + 1, If M = 0, then skip next instruction

A M - 1, If A = 0, then skip next instruction

M M - 1, If M = 0, then skip next instruction

If M.b = 0, then skip next instruction

If M.b = 1, then skip next instruction

If M(bank 0).b = 0, then skip next instruction

If M(bank 0).b = 1, then skip next instruction

PC15/14 RomPages1/0, PC13~PC0 d

Stack PC15~PC0, PC15/14 RomPages1/0, PC13~PC0 d

PC Stack, and to enable global interrupt

To push ACC and PFLAG (except NT0, NPD bit) into buffers.

To pop ACC and PFLAG (except NT0, NPD bit) from buffers.

1. “M” is system register or RAM. If “M” is system registers then “N” = 0, otherwise “N” = 1.

2. If branch condition is true then “S = 1”, otherwise “S = 0”.

Loading...

Loading...