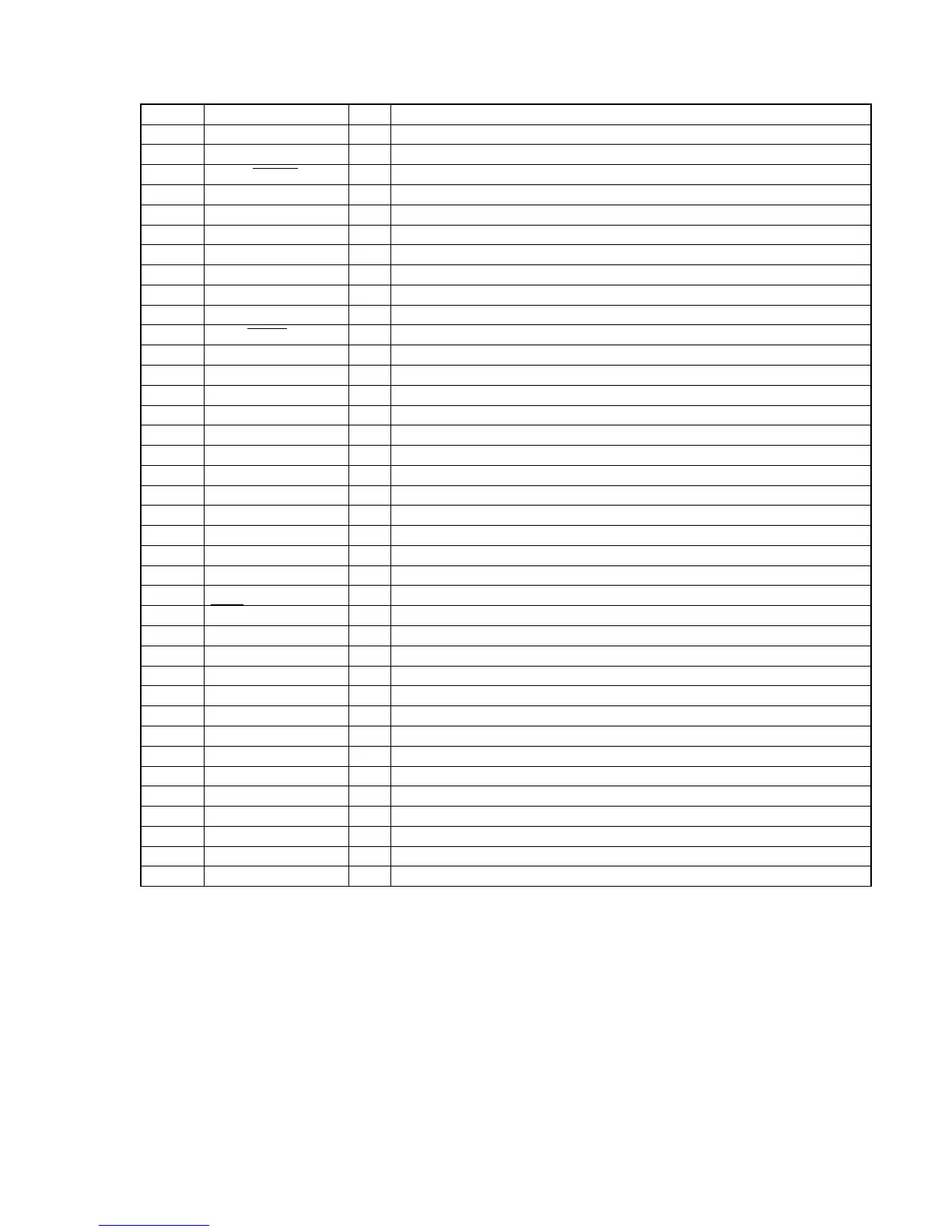

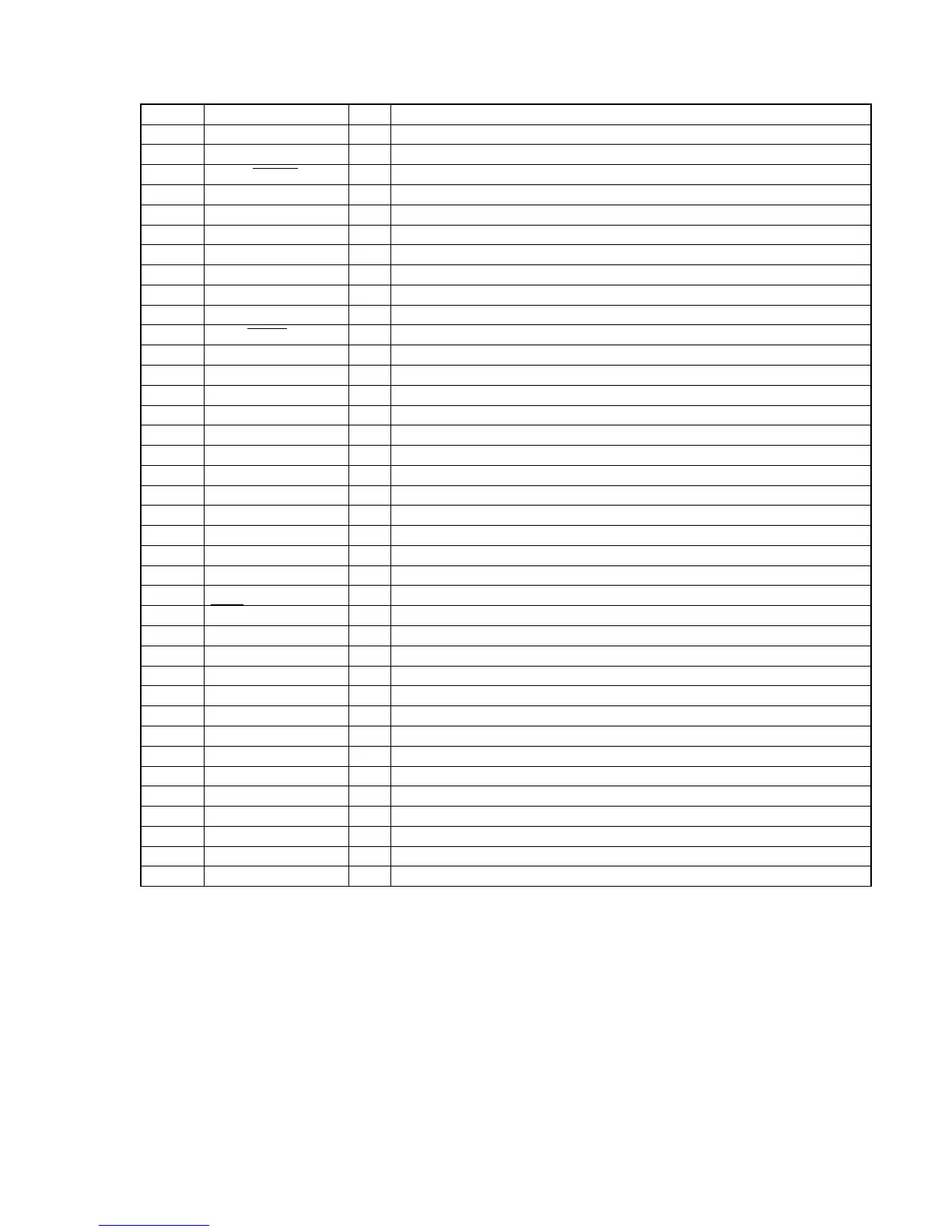

53

91 PGIO0 I/O Not used

92 PGIO8 I/O Not used

93 PGIO2/VSYNC/CSYNC O Vertical synchronized signal of video signal

94 AVDD PLL – +3.3V Power supply

95 NC – Not used

96 NC – Not used

97 NC – Not used

98 AGND PLL – Ground

99 VSS – Ground

100 NC – Not used

101 PGIO3/HSYNC O H. sync signal output

102 VDD3 – +3.3V Power supply

103 PGIO1/VCK-OUT I/O Not used

104 VSS – Ground

105 GCK I Not used

106 VCK-IN I Main clock for video signal processer

107 GCKOUT/DA-EMP O Not used

108 DA-LRCK O Digital Audio Left or Right channel selection clock

109 VDDMAX-OUT O Fix the maxium output voltage certain output pins (Connected to +5V)

110 DA-DATA O Digital Audio data

111 DA-BCK O Digital Audio bit clock

112 HD-OUT O Serial Data output from CL680 to the host MPU

113 HRDY O Ready signal CL680 is ready for communication to the host MPU

114 HINT O Request signal for interrupting the host MPU

115 CDG-SCK I/O Not used

116 VSS – Ground

117 HCK I Host clock : referance signal for the host bus interface

118 VDD3 – +3.3V Power supply

119 HD-IN I Serial Data output ftom the host MPU to CL680

120 VDD3 – +3.3V Power supply

121 HSEL I Select data or address of the host MPU

122 CDG-SDATA I Ground

123 CDG-VFSY I Ground

124 CDG-SOS1 I Ground

125 NC – Not used

126 NC – Not used

127 NC – Not used

128 NC – Not used

I/OPin Name FunctionPin No.

Loading...

Loading...