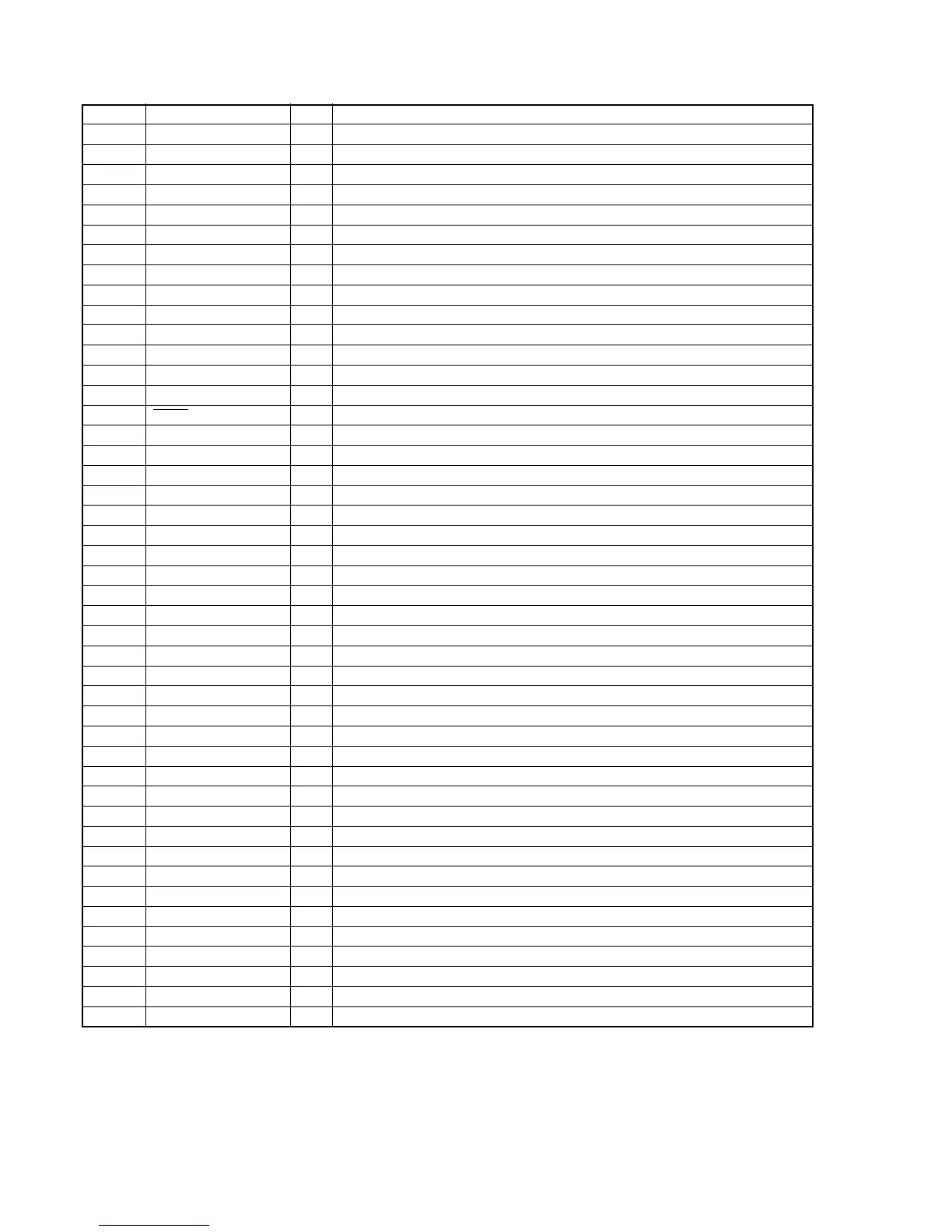

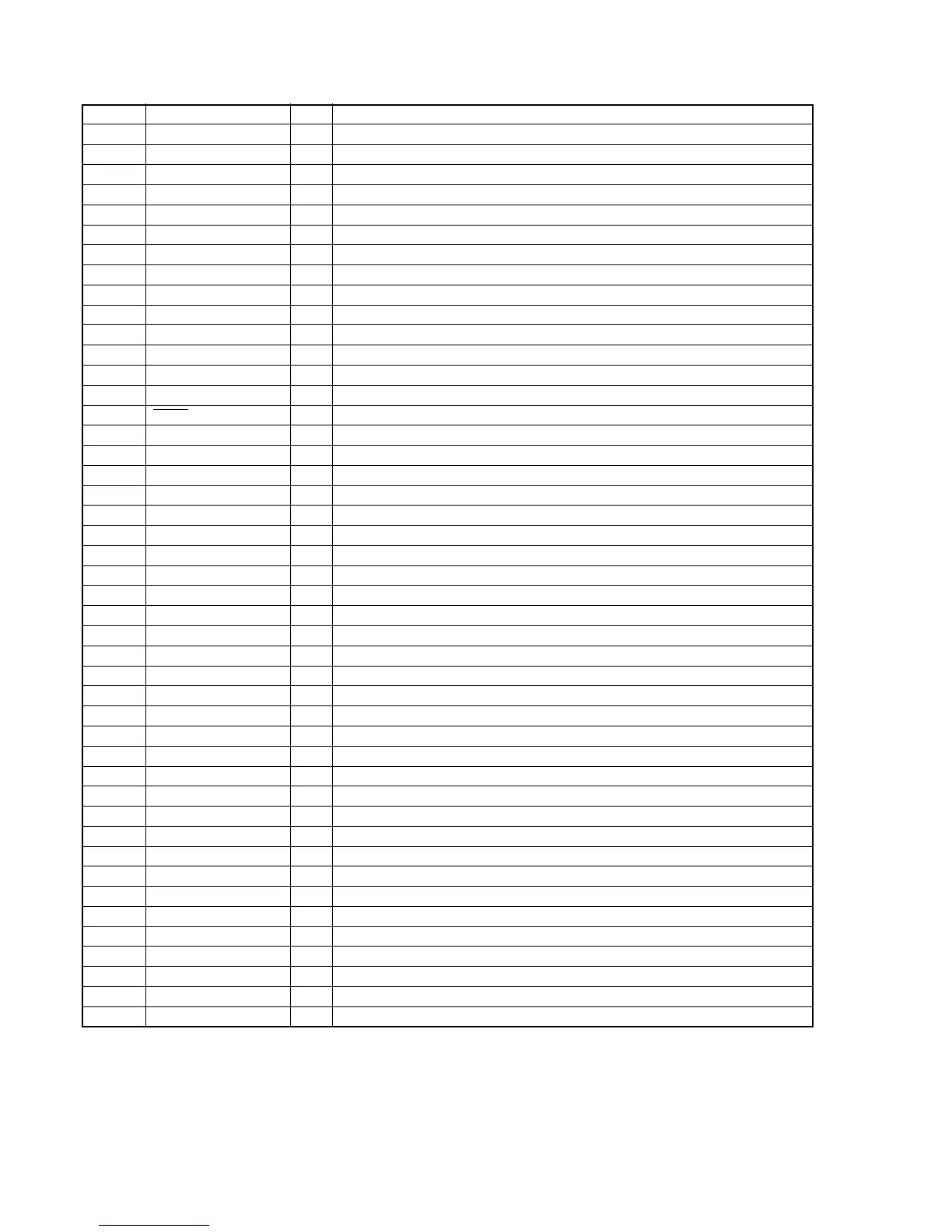

52

46 MA8 O Address data from CL680 to Microcode ROM/DRAM

47 VSS – Ground

48 MA7 O Address data from CL680 to Microcode ROM/DRAM

49 VDD3 – +3.3V Power supply

50 MA6 O Address data from CL680 to Microcode ROM/DRAM

51 MA5 O Address data from CL680 to Microcode ROM/DRAM

52 MA4 O Address data from CL680 to Microcode ROM/DRAM

53 VSS – Ground

54 MA3 O Address data from CL680 to Microcode ROM/DRAM

55 VDD3 – +3.3V Power supply

56 MA2 O Address data from CL680 to Microcode ROM/DRAM

57 MA1 O Address data from CL680 to Microcode ROM/DRAM

58 MA0 O Address data from CL680 to Microcode ROM/DRAM

59 PGIO7 I/O Not used

60 RESET I Reset signal input from the host MPU

61 VDDMAX-IN I Fix the maxium input voltage each input pin and I/O pin

62 NC – Not used

63 NC – Not used

64 NC – Not used

65 AGND DAC – Ground

66 AVDD DAC – +3.3V Power supply

67 COMPOS OUT O Not used

68 AGND DAC – Ground

69 Y-OUT O Luminance signal out

70 AVDD DAC – +3.3V Power supply

71 AGND DAC – Ground

72 RREF I Fix the video signal output level

73 (1.235V) VREF O Reference voltage (+1.235V)

74 AVDD DAC – +3.3V Power supply

75 C-OUT O Chrominance signal out

76 AGND DAC – Ground

77 (GCK INT) CLK SEL I GCK selection “H”; Internal, “L”; External

78 CLK SEL I DA-XCK selection (1)

79 CLK SEL I DA-XCK selection (2)

80 VSS – Ground

81 RESERVED I Selection the operation clock 42.336MHz

82 VDD3 – +3.3V Power supply

83 DA-EMP – Not used

84 RESERVED – Not used

85 AGND PLL – Ground

86 DA-XCLK I Main reference clock input (16.9344MHz=384fs)

87 AVDD PLL – +3.3V

88 PGIO4 I/O Not used

89 PGIO5 I/O Not used

90 PGIO6 I/O Not used

Pin No. Pin Name I/O Function

Loading...

Loading...