System Requirements

80 X72 Desiger’s Reference and User’s Guide 097-10603-01 Rev. A – November 2004

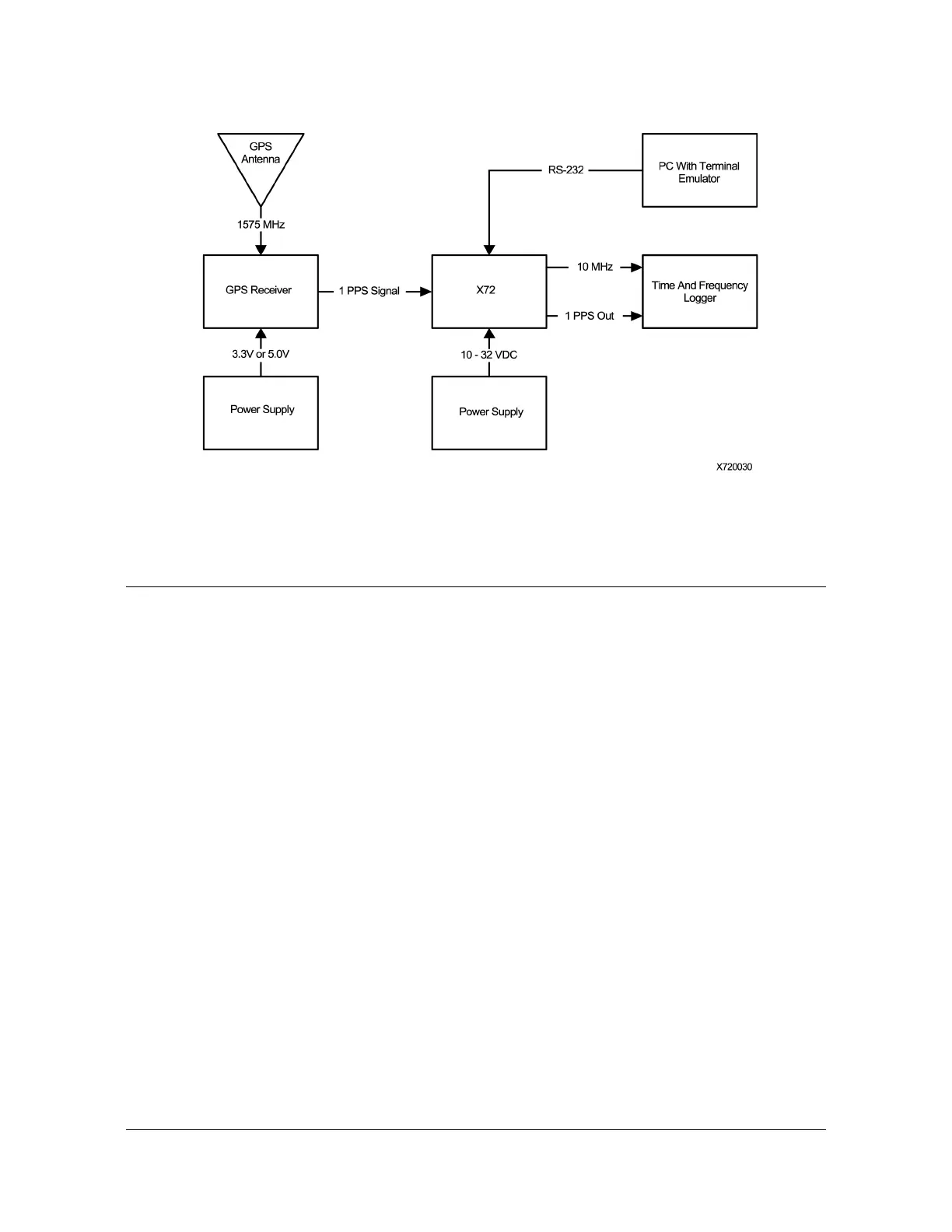

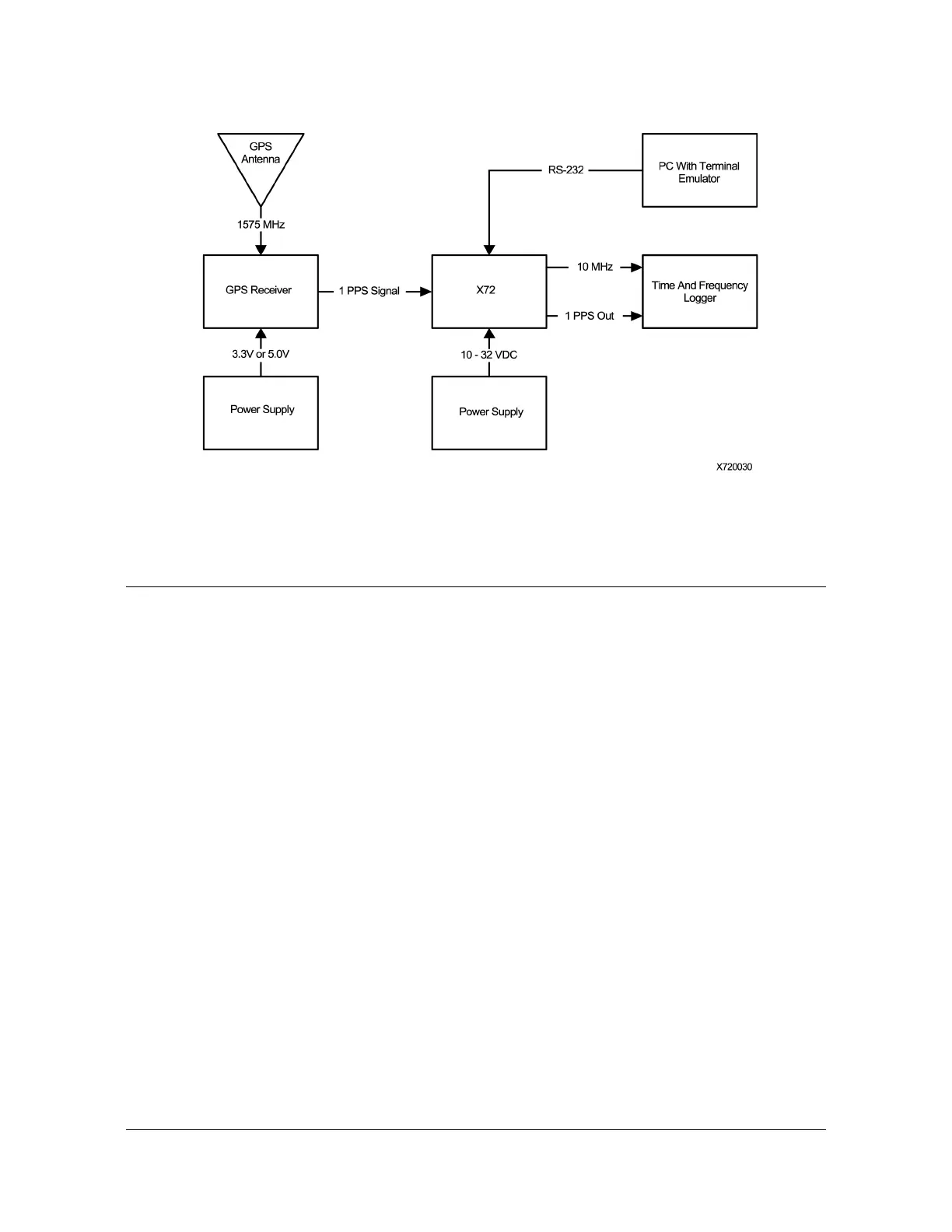

Figure D-2 Test Bench setup

System Requirements

The following information lists the requirements for 1 PPS setup and operation:

X72 with 1PPS output enabled.

GPS receiver with less than 300 ns noise.

One pulse per second input signals must have repeatable rise time with minimal

ringing and must conform to the following:

– 1PPS input can be driven by a standard 3.3 volt logic, 5 volt CMOS, or 5

volt TTL with normal operation at:

Input voltage logic high: 2.00V minimum

Input voltage logic high: 5.50V maximum

Input voltage logic low: 0.00V minimum

Input voltage logic low: 0.80V maximum

– Maximum DC overshoot must be limited to 5.5V or 10mA, whichever is

easiest to achieve.

– Maximum DC undershoot must be limited to –0.5V or 10mA, whichever is

easiest to achieve.

– Minimum pulse width (or hold time) of 50 ns.

Loading...

Loading...