AS+

AS-

=

Rcp

Rcp

Cac

VDDS_DDR

0.1 µF

A1

A2

AT

A2

AT

A1

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

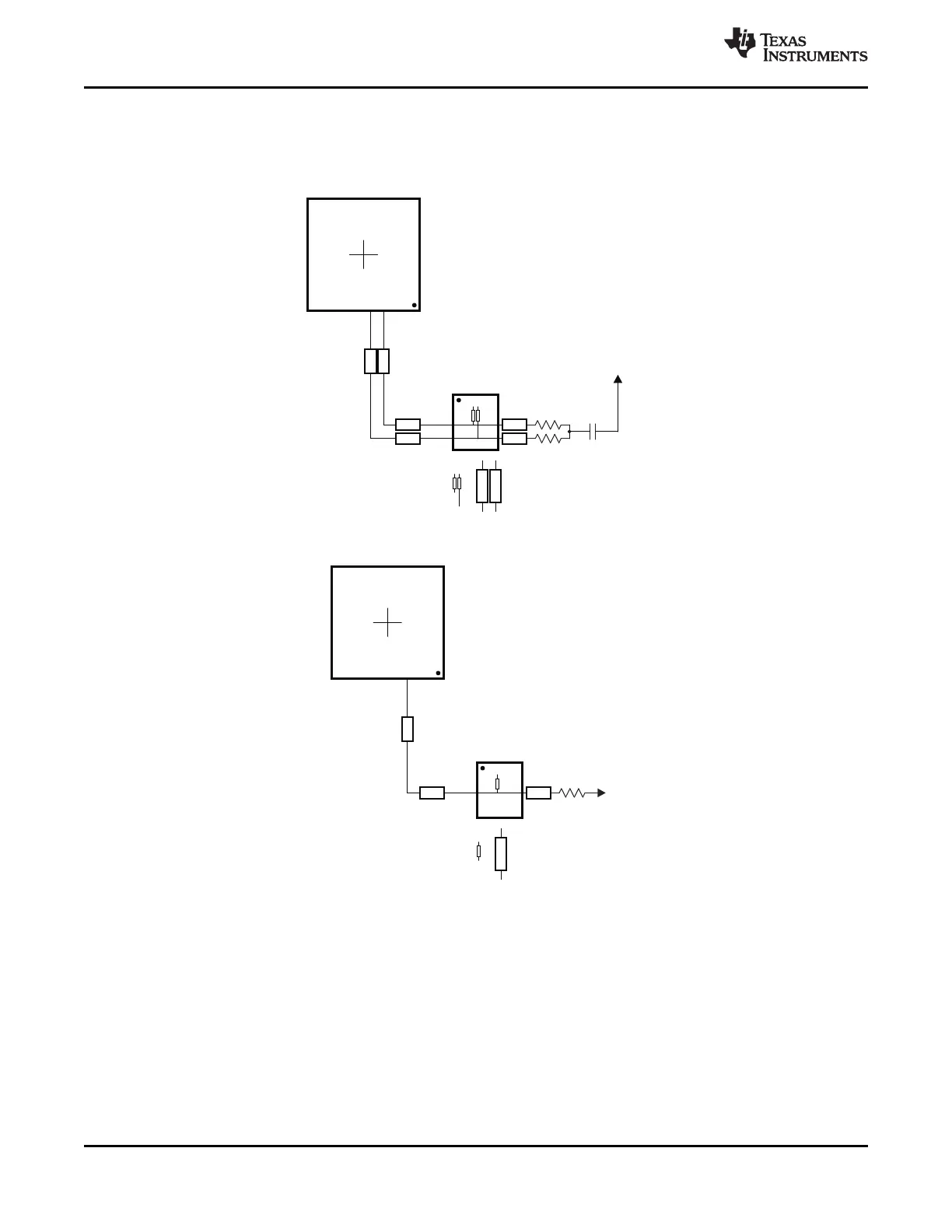

7.7.2.3.4.2.2 CK and ADDR_CTRL Routing, One DDR3 Device

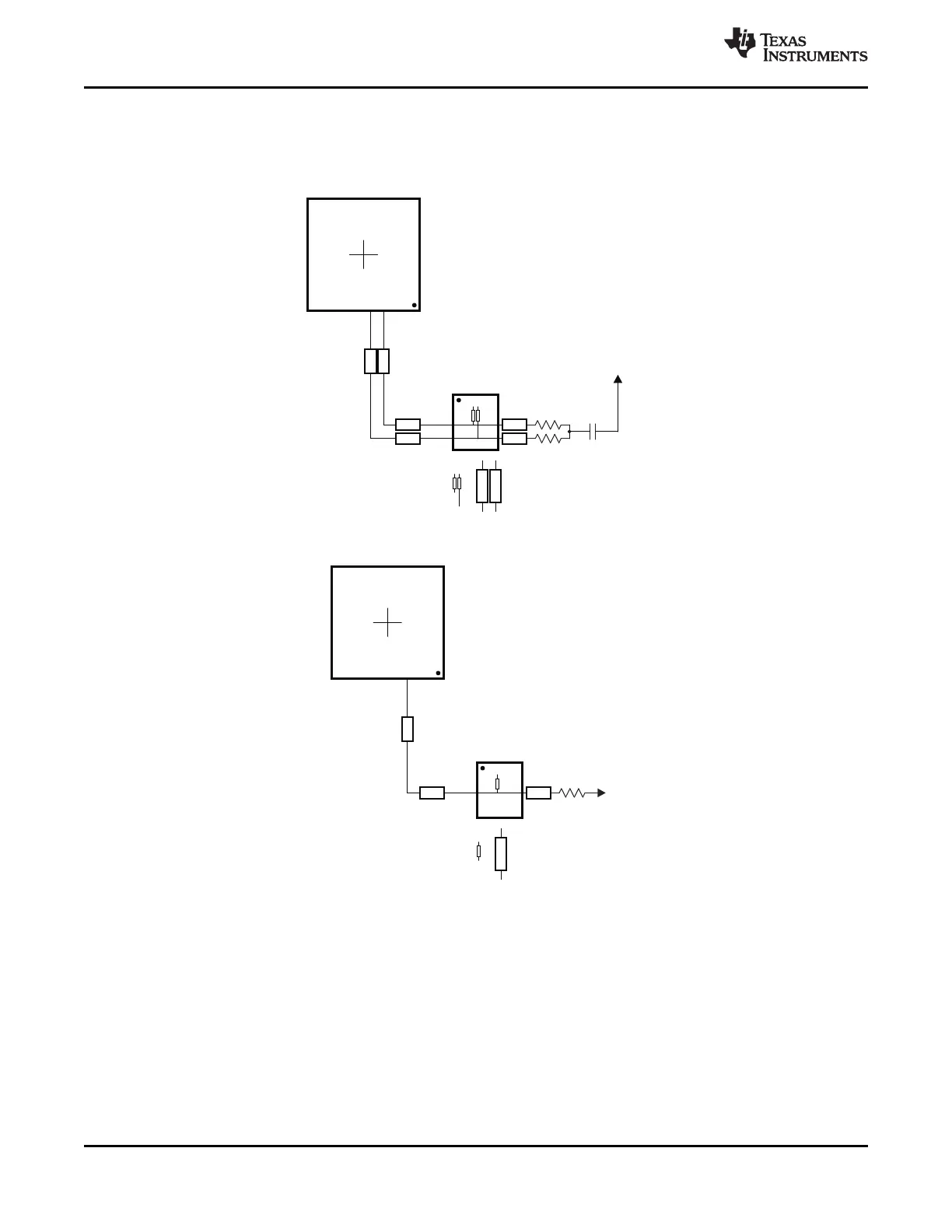

Figure 7-60 shows the CK routing for one DDR3 device. Figure 7-61 shows the corresponding

ADDR_CTRL routing.

Figure 7-60. CK Routing for One DDR3 Device

Figure 7-61. ADDR_CTRL Routing for One DDR3 Device

7.7.2.3.5 Data Topologies and Routing Definition

No matter the number of DDR3 devices used, the data line topology is always point to point, so its

definition is simple.

7.7.2.3.5.1 DQS[x] and DQ[x] Topologies, Any Number of Allowed DDR3 Devices

DQS[x] lines are point-to-point differential, and DQ[x] lines are point-to-point singled ended. Figure 7-62

and Figure 7-63 show these topologies.

186 Peripheral Information and Timings Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...