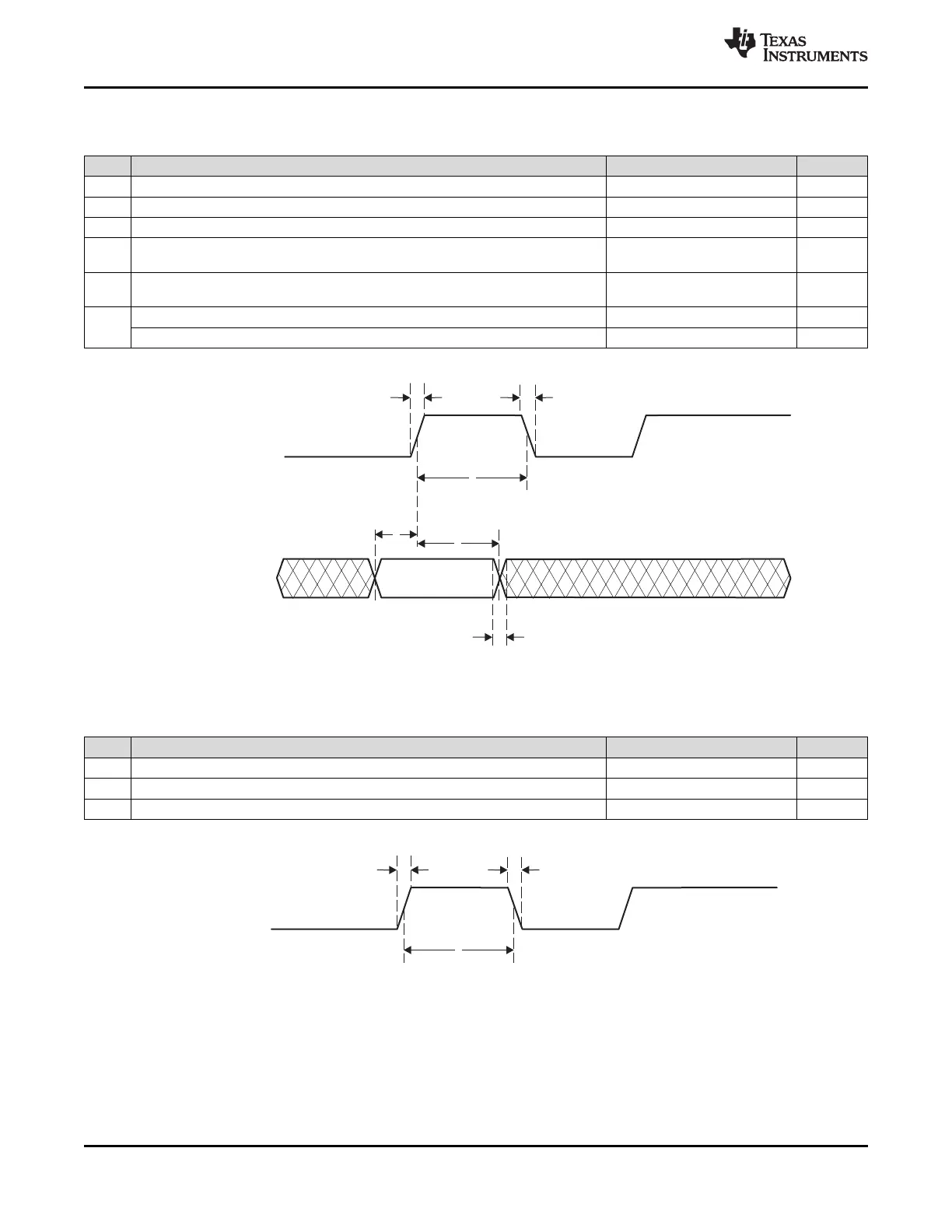

EDIO_SOF

3

2

6

5

1

4

EDIO_DATA_IN[7:0]

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

Table 7-100. PRU-ICSS ECAT Timing Requirements – Input Validated with Start of Frame (SOF)

(see Figure 7-104)

NO. MIN MAX UNIT

1 t

w(EDIO_SOF)

Pulse duration, EDIO_SOF 4 × P

(1)

5 × P

(1)

ns

2 t

r(EDIO_SOF)

Rising time, EDIO_SOF 1.00 3.00 ns

3 t

f(EDIO_SOF)

Falling time, EDIO_SOF 1.00 3.00 ns

4 t

su(EDIO_DATA_IN-

Setup time, EDIO_DATA_IN valid before EDIO_SOF 20.00 ns

EDIO_SOF)

active edge

5 t

h(EDIO_SOF-EDIO_DATA_IN)

Hold time, EDIO_DATA_IN valid after EDIO_SOF active 20.00 ns

edge

6 t

r(EDIO_DATA_IN)

Rising time, EDIO_DATA_IN 1.00 3.00 ns

t

f(EDIO_DATA_IN)

Falling time, EDIO_DATA_IN 1.00 3.00 ns

(1) P = PRU-ICSS IEP clock source period.

Figure 7-104. PRU-ICSS ECAT Input Validated with SOF

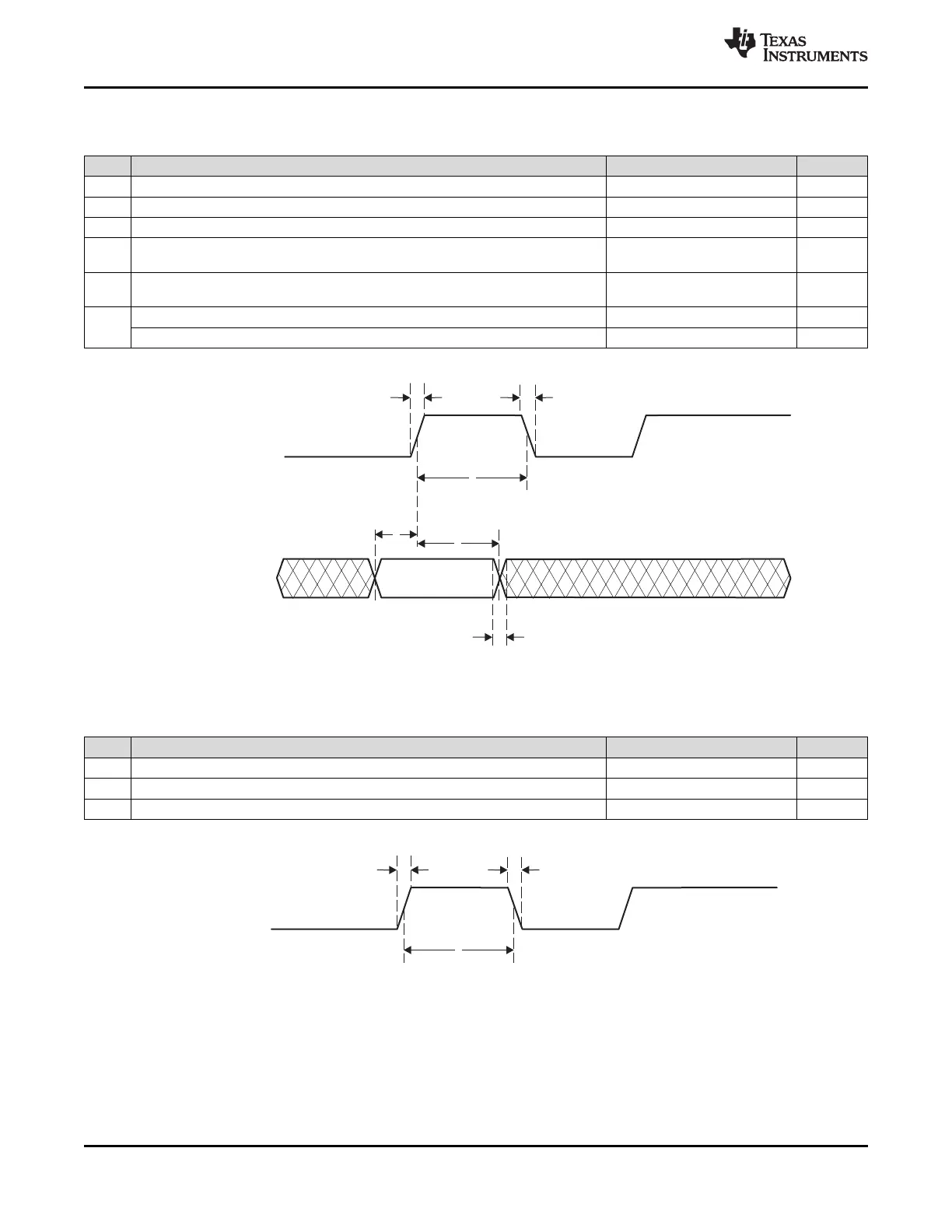

Table 7-101. PRU-ICSS ECAT Timing Requirements - LATCHx_IN

(see Figure 7-105)

NO. MIN MAX UNIT

1 t

w(EDC_LATCHx_IN)

Pulse duration, EDC_LATCHx_IN 3 × P

(1)

ns

2 t

r(EDC_LATCHx_IN)

Rising time, EDC_LATCHx_IN 1.00 3.00 ns

3 t

f(EDC_LATCHx_IN)

Falling time, EDC_LATCHx_IN 1.00 3.00 ns

(1) P = PRU-ICSS IEP clock source period.

Figure 7-105. PRU-ICSS ECAT LATCHx_IN Timing

228 Peripheral Information and Timings Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...