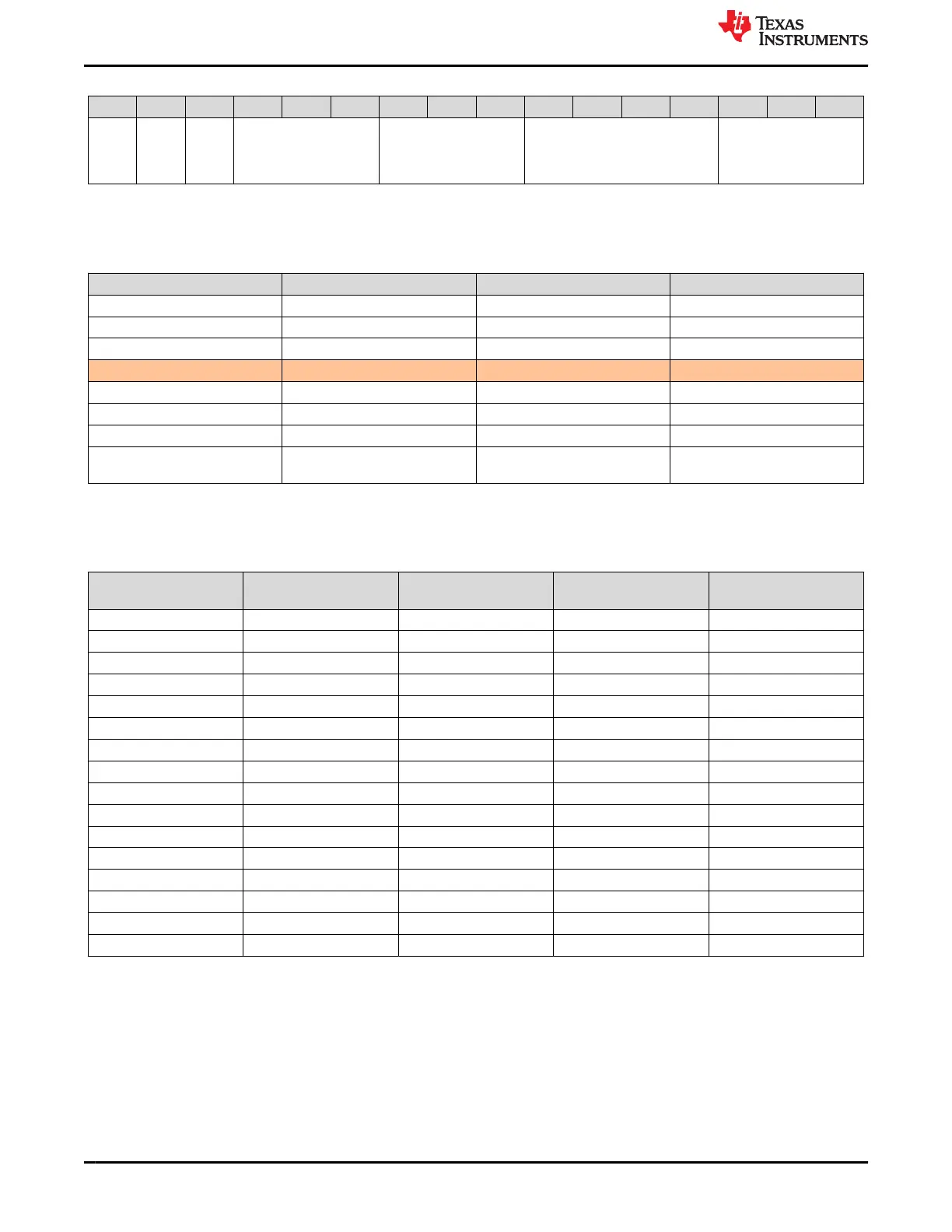

Table 3-7. BOOTMODE Bits

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RSVD RSVD Backup

Boot

Mode

Config

Backup Boot Mode Primary Boot Mode

Config

Primary Boot Mode PLL Config

BOOTMODE[2:0] - Denote system clock frequency for PLL configuration. By default, these bits are set for 25

MHz.

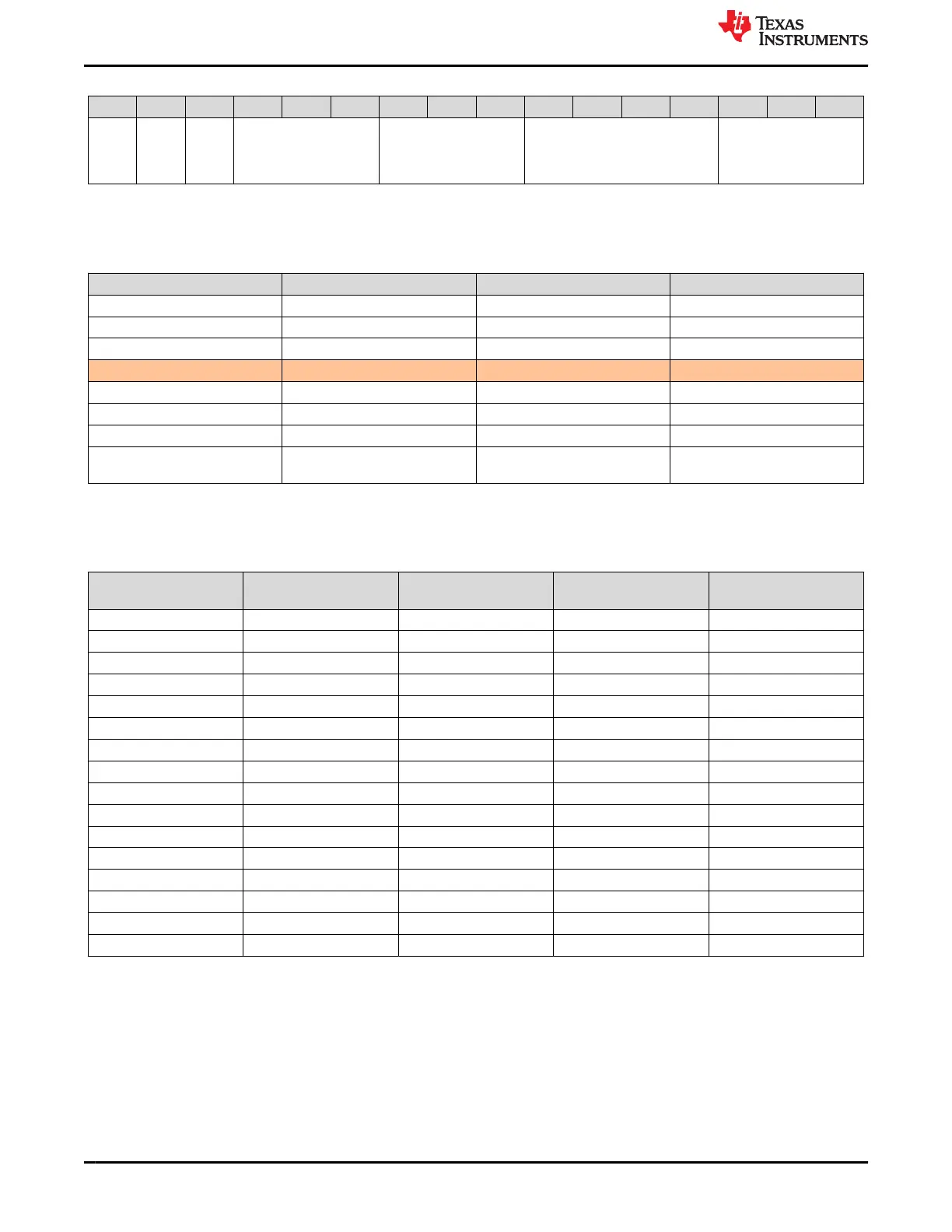

Table 3-8. PLL Reference Clock Selection BOOTMODE[2:0]

SW2.3 SW2.2 SW2.1 PLL REF CLK (MHz)

off off off 19.2

off off on 20

off on off 24

off on on 25

on off off 26

on off on 27

on on off RSVD

on on on No PLL Configuration Done

(slow speed backup)

BOOTMODE[6:3] - This provides primary boot mode configuration to select the requested boot mode after POR,

that is, the peripheral/memory to boot from.

Table 3-9. Boot Device Selection BOOTMODE[6:3]

SW2.7 SW2.6 SW2.5 SW2.4

Primary Boot Device

Selected

off off off off RSVD

off off on on OSPI

off off on off QSPI

off off on on SPI

off on off off RSVD

off on off on RSVD

off on on off I2C

off on on on UART

on off off off MMC/SD Card

on off off on eMMC

on off on off USB

on off on on GPMC NAND

on on off off GPMC NOR

on on off on PCIe

on on on off xSPI

on on on on No-boot / Dev-boot

System Description www.ti.com

20 AM64x/AM243x GP EVM User's Guide SPRUIX0C – FEBRUARY 2021 – REVISED JUNE 2021

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Loading...

Loading...