General-Purpose Timers

Timer Control Register

Timer Control Register

(EVA)

(EVA)

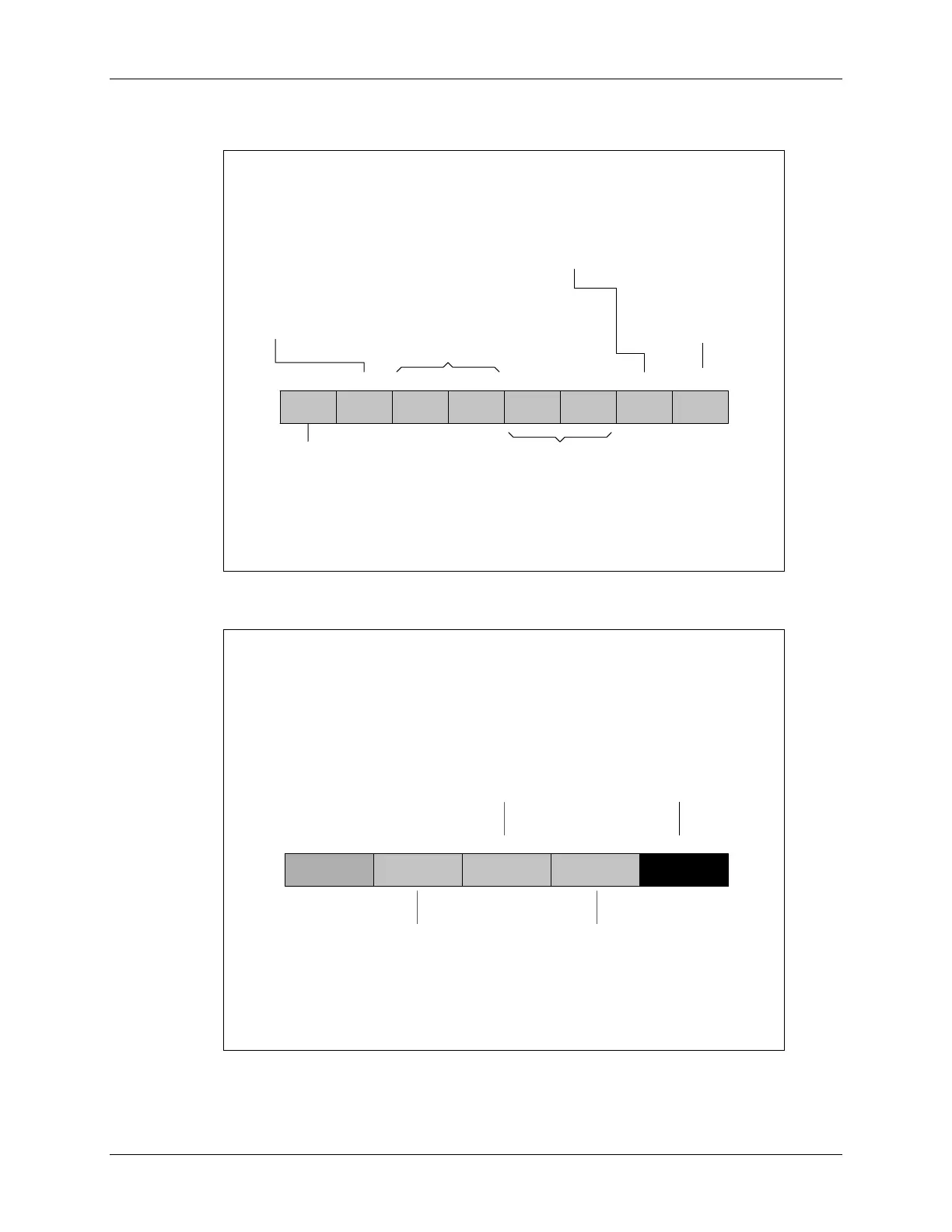

T1CON @ 0x007404 / T2CON @ 0x007408

T1CON @ 0x007404 / T2CON @ 0x007408

(lab file:

(lab file:

Ev

Ev

.c)

.c)

T2SWT1

T2SWT1

7

7

6

6

5

5

4

4

2

2

0

0

TENABLE

TENABLE

TCLKS1

TCLKS1

TCLKS0

TCLKS0

TCLD1

TCLD1

SELT1PR

SELT1PR

TECMPR

TECMPR

TCLD0

TCLD0

1

1

3

3

Lower Byte:

Lower Byte:

Start with Timer 1

Start with Timer 1

0 = use own TENABLE

0 = use own TENABLE

1 = use Timer 1 TENABLE

1 = use Timer 1 TENABLE

(bit reserved in T1CON)

(bit reserved in T1CON)

Timer Enable

Timer Enable

0 = timer disable

0 = timer disable

1 = timer enable

1 = timer enable

Timer Clock Source

Timer Clock Source

00 = internal (HSPCLK)

00 = internal (HSPCLK)

01 = external TCLKIN pin

01 = external TCLKIN pin

10 = reserved

10 = reserved

11 = QEP

11 = QEP

Compare Register Reload Condition

Compare Register Reload Condition

00 = when counter equals zero (underflow)

00 = when counter equals zero (underflow)

01 = when counter equals zero or period

01 = when counter equals zero or period

reg

reg

10 = immediately

10 = immediately

11 = reserved

11 = reserved

Timer Compare Operation Enable

Timer Compare Operation Enable

0 = disable

0 = disable

1 = enable

1 = enable

Period Register Select

Period Register Select

0 = use own per. reg.

0 = use own per. reg.

1 = use Timer 1 per.

1 = use Timer 1 per.

reg

reg

(bit reserved in T1CON)

(bit reserved in T1CON)

Extension Control Register A

Extension Control Register A

(EVA)

(EVA)

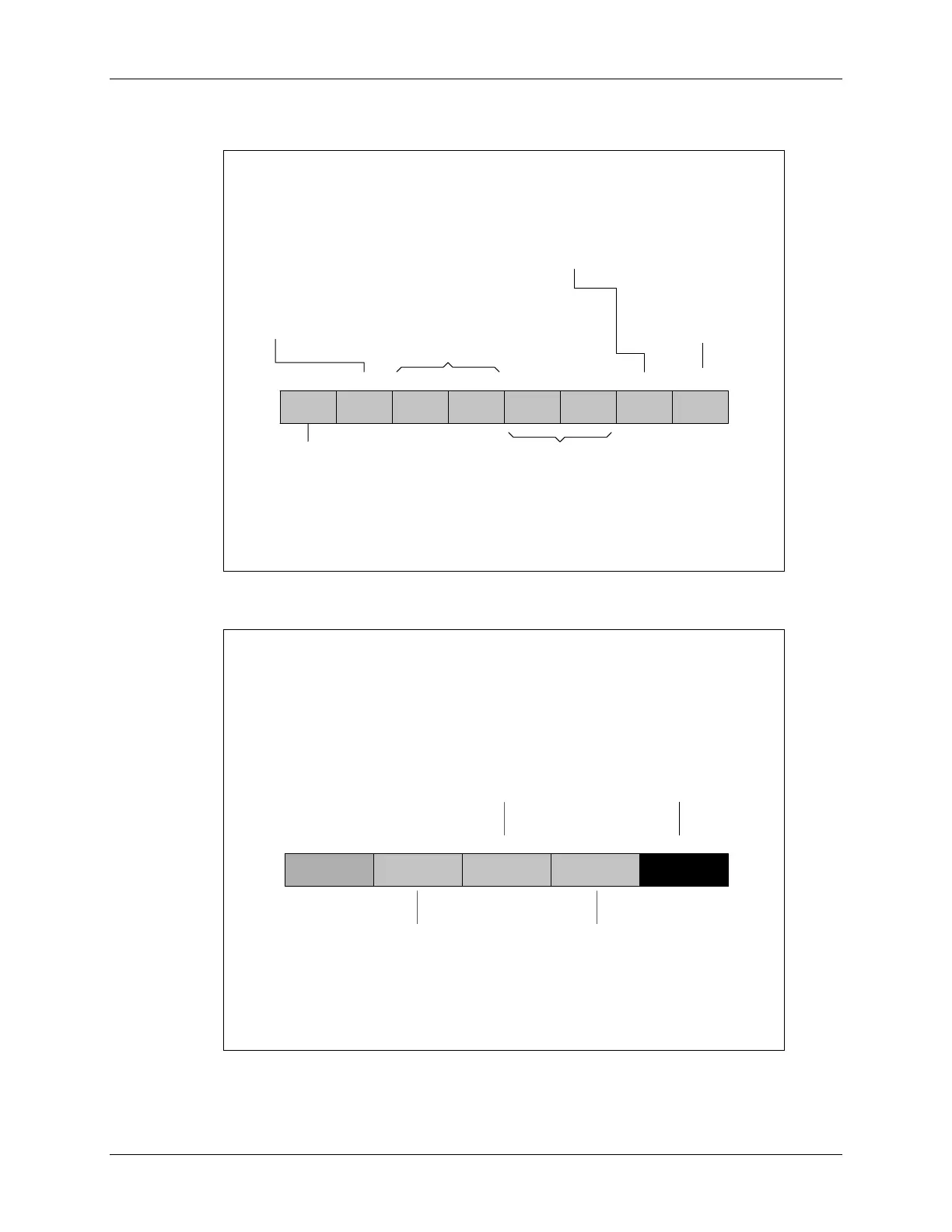

EXTCONA @ 0x007409

EXTCONA @ 0x007409

(lab file:

(lab file:

Ev

Ev

.c)

.c)

INDCOEQEPIQUAL

QEPIEEVSOCE

reserved

1

1

0

0

2

2

3

3

15

15

-

-

4

4

Independent Compare

Independent Compare

Output Enable Mode

Output Enable Mode

0 = disable

0 = disable

1 = enable

1 = enable

QEP Index Enable

0 = disable

1 = enable

CAP3/QEPI Index

Qualification Mode

0 = off

1 = on

EV Start-of-Conversion

Output Enable

0 = disable

1 = enable

C28x - Event Manager 7 - 15

Loading...

Loading...