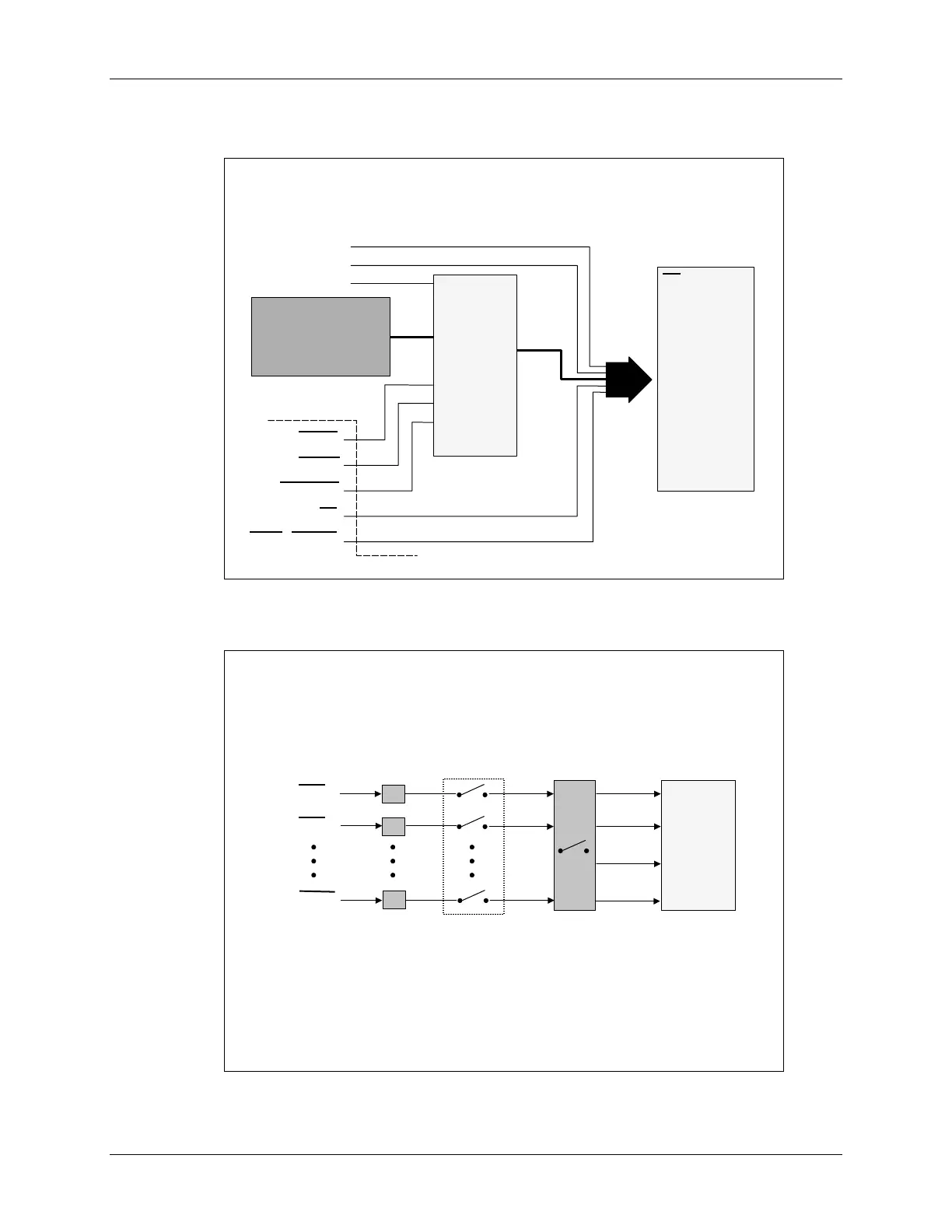

Interrupt Sources

Interrupt Sources

Interrupt Sources

Interrupt Sources

EV and Non

EV and Non

-

-

EV

EV

Peripherals

Peripherals

(EV, ADC, SPI,

(EV, ADC, SPI,

SCI,

SCI,

McBSP

McBSP

, CAN)

, CAN)

Internal Sources

Internal Sources

External Sources

External Sources

XINT1

XINT1

XINT2

XINT2

PDPINTx

PDPINTx

RS

RS

XNMI_XINT13

XNMI_XINT13

NMI

NMI

C28x CORE

C28x CORE

INT1

INT1

INT13

INT13

INT2

INT2

INT3

INT3

INT12

INT12

INT14

INT14

RS

RS

•

•

•

•

•

•

PIE

PIE

(Peripheral

(Peripheral

Interrupt

Interrupt

Expansion)

Expansion)

TINT2

TINT2

TINT1

TINT1

TINT0

TINT0

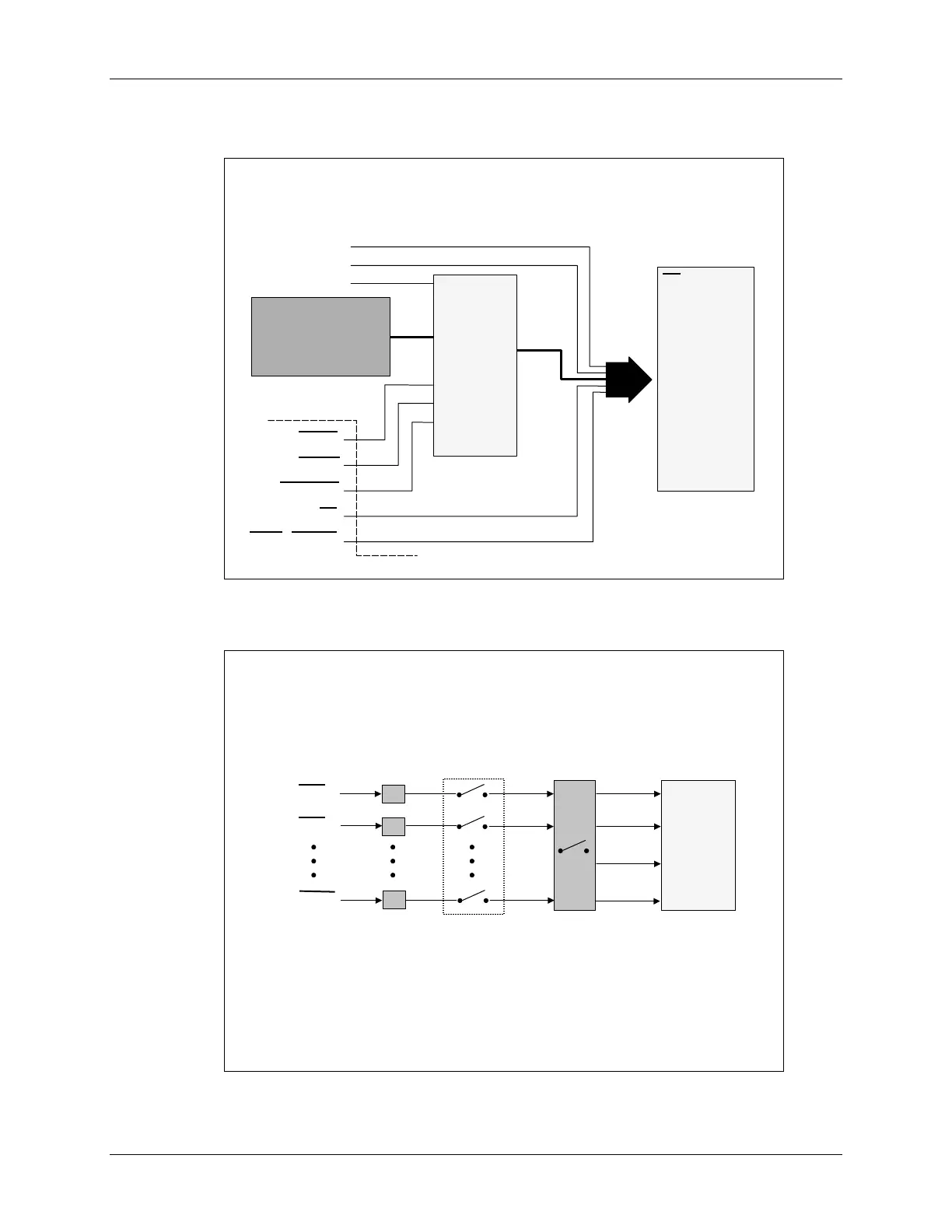

Interrupt Processing

A valid signal on a specific interrupt line causes the latch

A valid signal on a specific interrupt line causes the latch

to display a “1” in the appropriate bit

to display a “1” in the appropriate bit

Maskable

Maskable

Interrupt Processing

Interrupt Processing

Conceptual Core Overview

Conceptual Core Overview

1

1

0

0

1

1

(

(

IFR

IFR

)

)

“Latch”

“Latch”

INT1

INT1

INT2

INT2

INT14

INT14

Core

Core

Interrupt

Interrupt

C28x

C28x

Core

Core

(

(

INTM

INTM

)

)

“Global Switch”

“Global Switch”

(

(

IER

IER

)

)

“Switch”

“Switch”

If the individual and global switches are turned “on” the

If the individual and global switches are turned “on” the

interrupt reaches the core

interrupt reaches the core

C28x - Reset and Interrupts 4 - 7

Loading...

Loading...