Compare Units

precise control of gate timing requirements. In addition, the dead time is typically specified with

a single program variable that is easily changed for different power converters or adapted on-line.

Dead

Dead

-

-

Band Timer Control Register

Band Timer Control Register

(EVA)

(EVA)

DBTCONA @ 0x007415

DBTCONA @ 0x007415

(lab file:

(lab file:

Ev

Ev

.c)

.c)

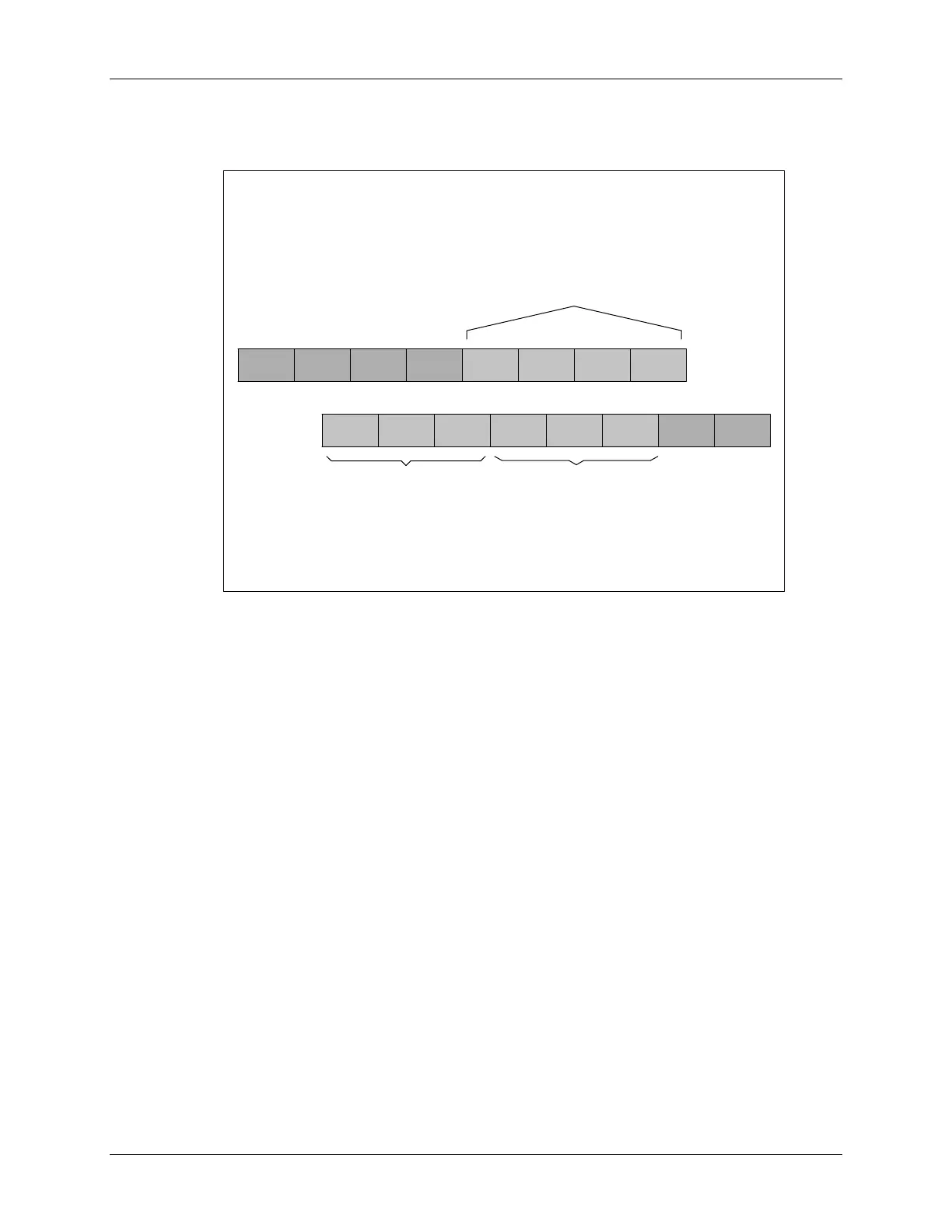

EDBT3

76 54 2 0

EDBT2 EDBT1 DBTPS2 DBTPS1 reservedreserved

13

15 14 13 12 10 8

DBT3 DBT0DBT1DBT2

911

DB Timer Enable

0 = disable

1 = enable

DB Timer Prescaler

000 = 1 100 = 16

001 = 2 101 = 32

010 = 4 110 = 32

011 = 8 111 = 32

DB Timer Period

dead time = DB period * DB prescaler * CPUCLK period

reserved reserved reserved reserved

DBTPS0

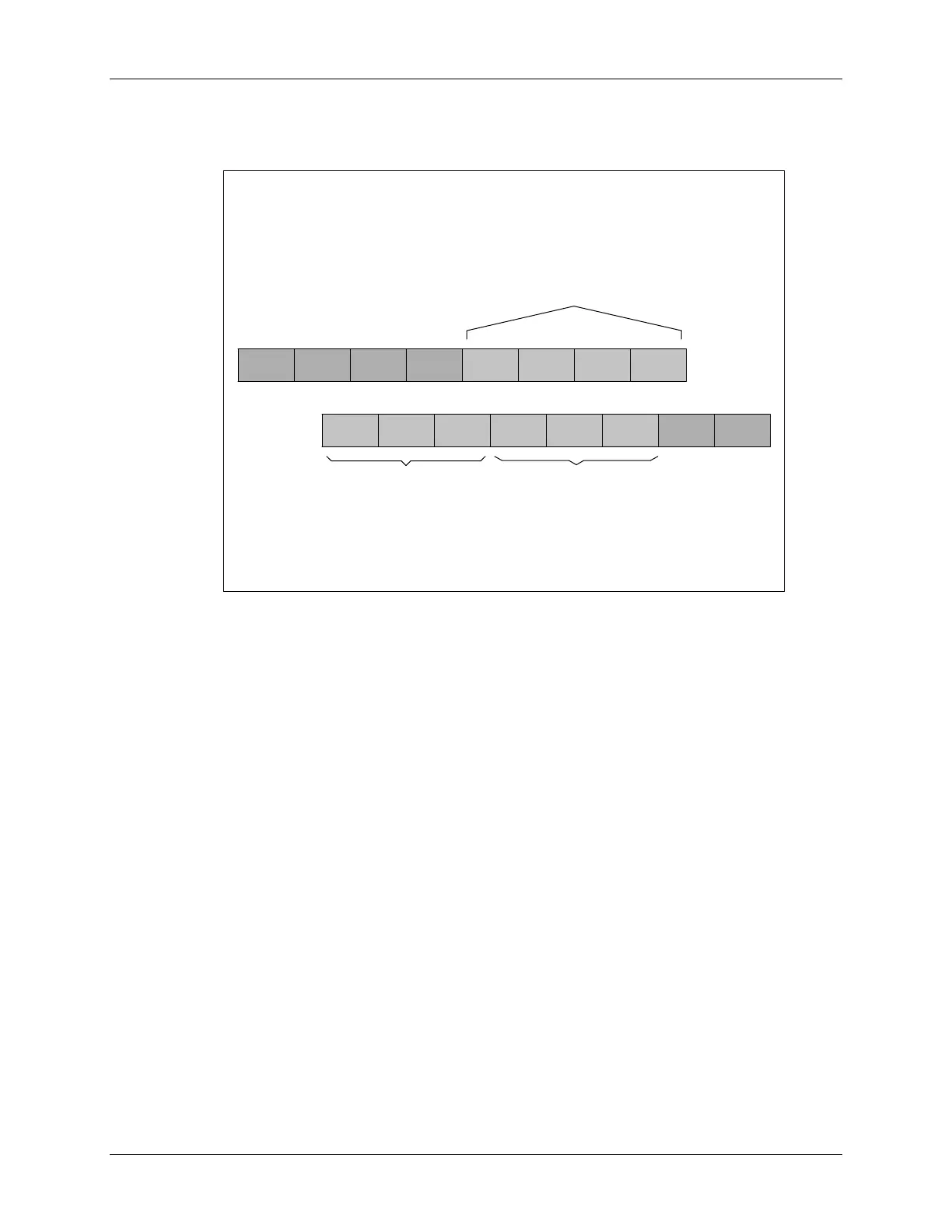

Each compare unit has its own dead-band timer, but shares the clock prescaler unit and the dead-

band period with the other compare units. Dead-band can be individually enabled for each

compare unit by setting bits 5, 6, and 7 in the DBTCONA register for EVA and DBTCONB for

EVB.

The minimum achievable non-zero dead time is one CPU clock cycle (e.g. 50 ns), obtained by

choosing the x/1 prescale option, and setting the DB period to 1 (i.e. DBTCONx.11-8 = 0001,

where x is A for EVA and x is B for EVB).

7 - 24 C28x - Event Manager

Loading...

Loading...