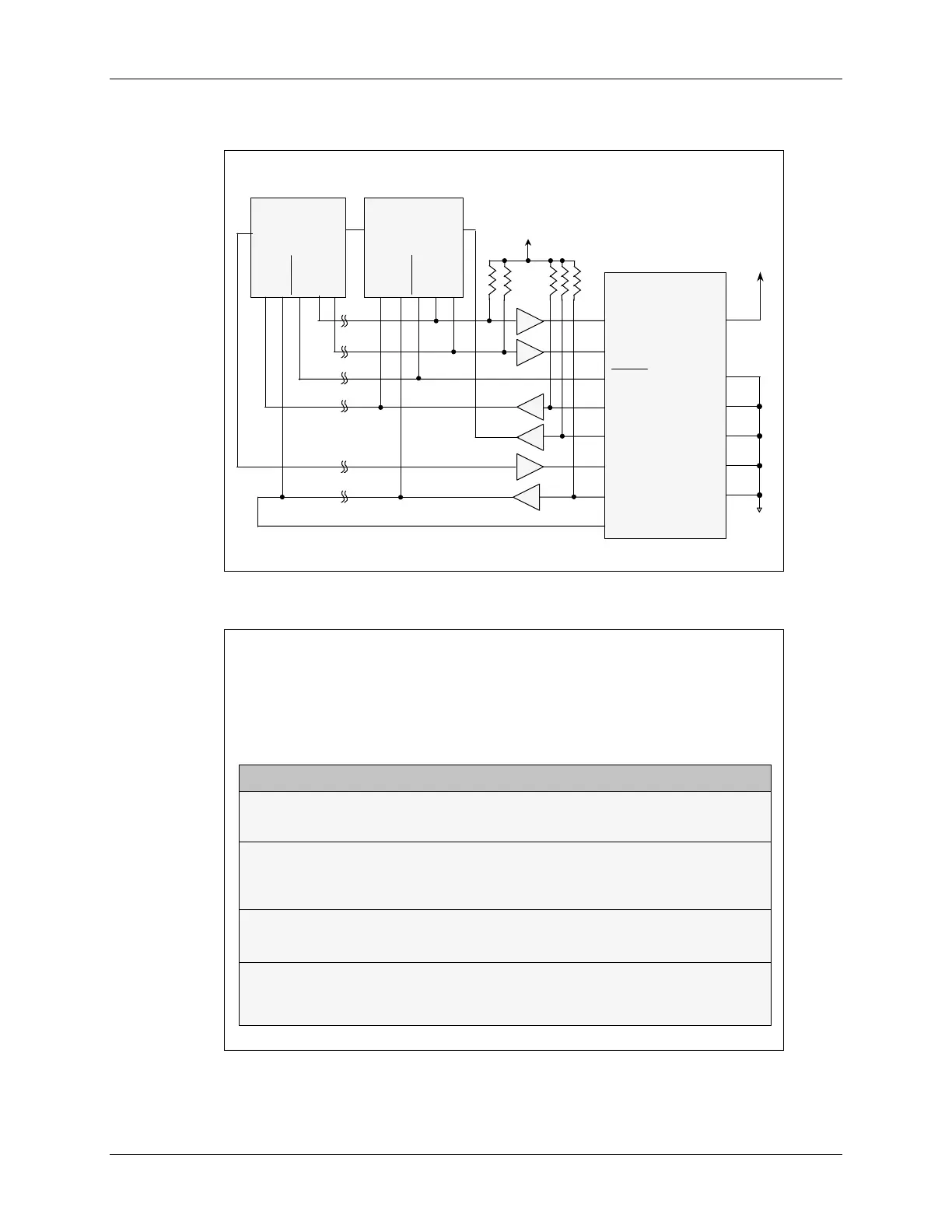

Emulation and Analysis Block

Multiprocessor Connections

Multiprocessor Connections

EMU0

EMU0

EMU1

EMU1

TRST

TRST

TMS

TMS

TDI

TDI

TDO

TDO

TCK

TCK

TCK_RET

TCK_RET

13

13

14

14

2

2

1

1

3

3

7

7

11

11

9

9

GND

GND

PD

PD

Vcc

Vcc

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

5

5

4

4

6

6

8

8

10

10

12

12

Emulator Header

Emulator Header

TMS

TMS

TCK

TCK

EMU0

EMU0

EMU1

EMU1

TDO

TDO

TDI

TDI

TDO

TDO

TDI

TDI

Vcc

Vcc

JTAG Device

JTAG Device

JTAG Device

JTAG Device

TMS

TMS

TCK

TCK

EMU0

EMU0

EMU1

EMU1

TRST

TRST

TRST

TRST

On

On

-

-

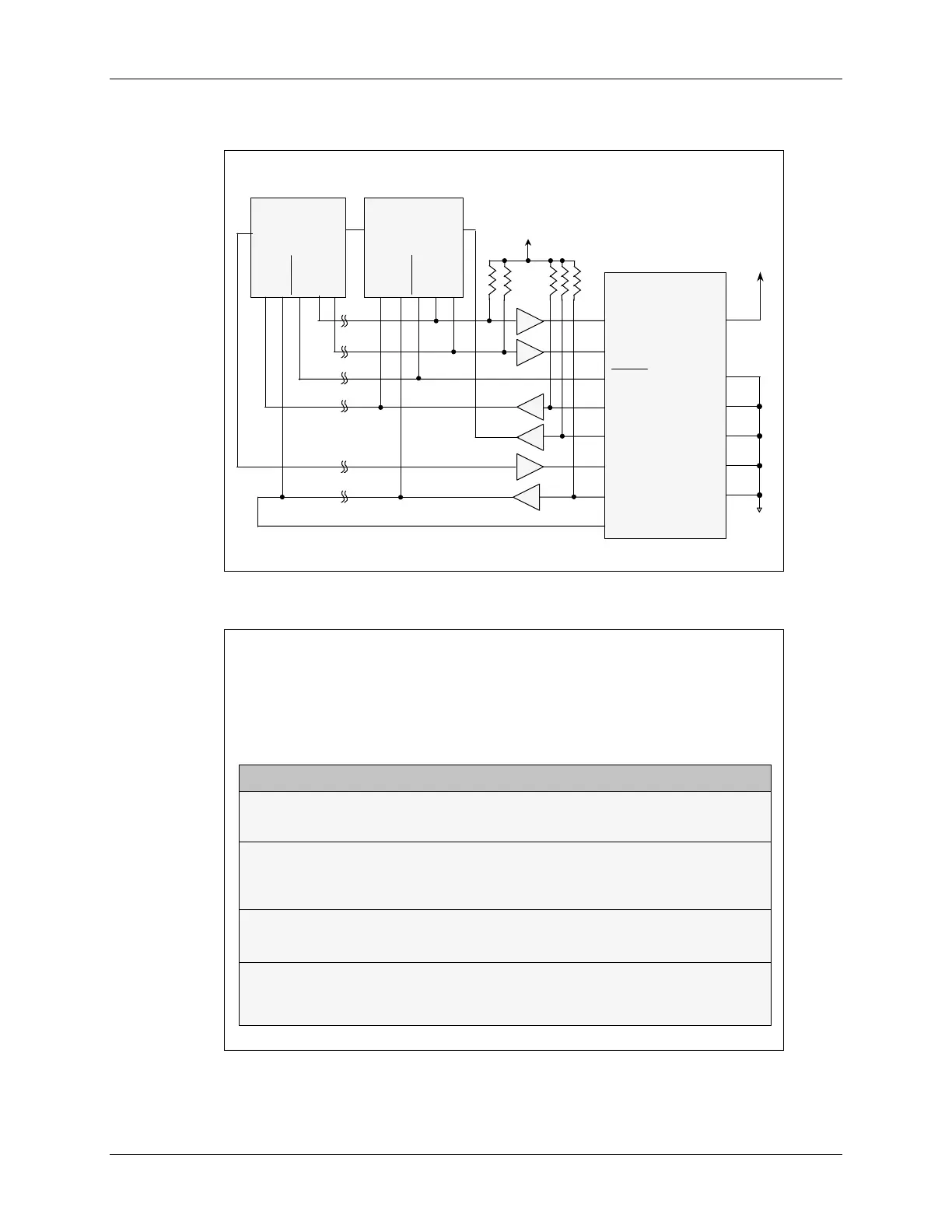

Chip Emulation Analysis Block:

Chip Emulation Analysis Block:

Capabilities

Capabilities

Two hardware analysis units can be configured to provide

Two hardware analysis units can be configured to provide

any one of the following advanced debug features:

any one of the following advanced debug features:

Halt program execution after a

Halt program execution after a

specific value is written to a variable

specific value is written to a variable

1 Address Watchpoint with Data

1 Address Watchpoint with Data

Halt on a specified instruction only

Halt on a specified instruction only

after some other specific routine has

after some other specific routine has

executed

executed

1 Pair Chained Breakpoints

1 Pair Chained Breakpoints

Halt on a specified instruction

Halt on a specified instruction

(for debugging in Flash)

(for debugging in Flash)

2 Hardware Breakpoints

2 Hardware Breakpoints

A memory location is getting

A memory location is getting

corrupted. Halt the processor when

corrupted. Halt the processor when

any value is written to this location

any value is written to this location

2 Address Watchpoints

2 Address Watchpoints

Debug Activity

Debug Activity

Analysis Configuration

Analysis Configuration

⇒

⇒

⇒

⇒

⇒

⇒

⇒

⇒

10 - 4 C28x - System Design

Loading...

Loading...