Serial Peripheral Interface (SPI)

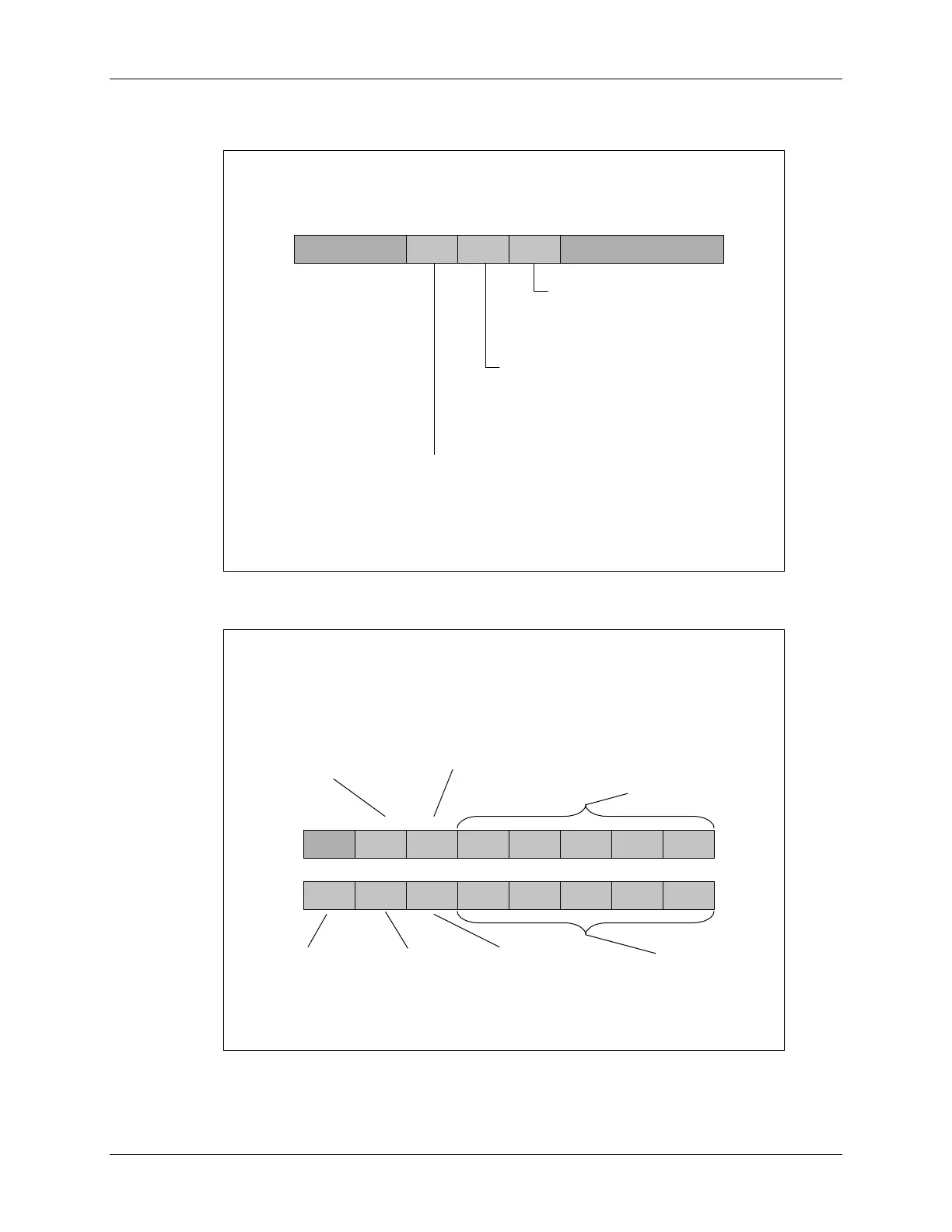

SPI-A Status Register

SPISTS @ 0x007042

7 6 4-0

SPI INT FLAG (read only)

• Set to 1 when transfer completed

• Interrupt requested if SPI INT ENA

bit set (SPICTL.0)

• Cleared by reading SPIBRXUF

RECEIVER OVERRUN (read/clear only)

• Set to 1 if next reception completes before SPIRXBUF read

• Interrupt requested if OVERRUN INT ENA bit set (SPICTL.4)

• Cleared by writing a 1

reservedreserved

15-8

TX BUF FULL (read only)

• Set to 1 when char written

to SPITXBUF

• Cleared when char in SPIDAT

5

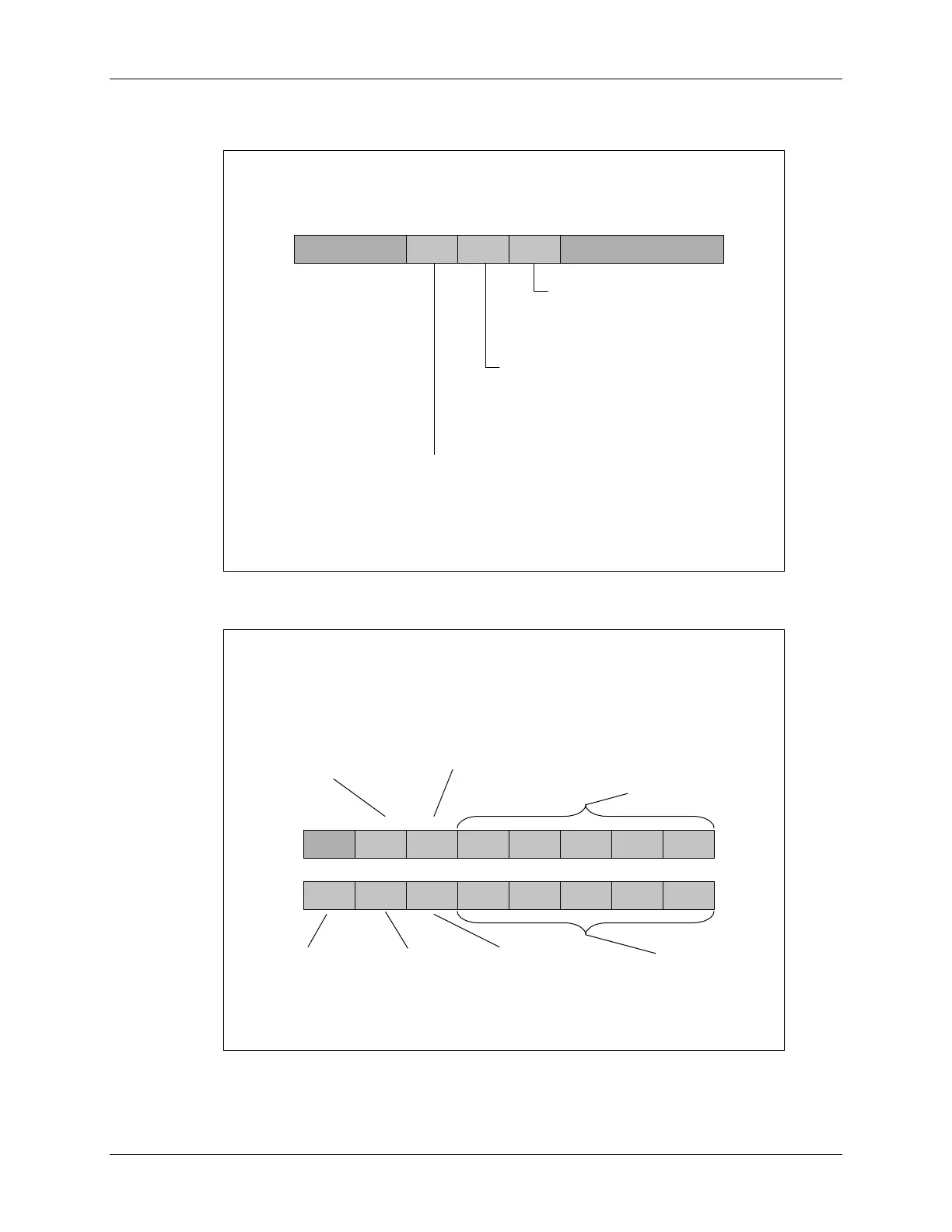

SPI-A FIFO Transmit Register

SPIFFTX @ 0x00704A

0

TXFFIL2

SPIFFEN TXFFST0TXFFST3

TXFFIEN

1234567

89101112131415

TXFFIL0TXFFIL1TXFFIL4 TXFFIL3

TXFFST1

TXFFINT

CLR

TXFFST2

TXFFINT

TXFFST4

TXFIFO

RESET

reserved

TX FIFO Status (read-only)

00000 TX FIFO empty

00001 TX FIFO has 1 word

00010 TX FIFO has 2 words

00011 TX FIFO has 3 words

10000 TX FIFO has 16 words

.

.

.

.

.

.

.

.

.

TX FIFO Interrupt Level

Interrupt when TXFFST4-0

and TXFFIL4-0 match

SPI FIFO

Enhancements

0 = disable

1 = enable

TX FIFO Reset

0 = reset (pointer to 0)

1 = enable operation

TX FIFO

Interrupt

(on match)

Enable

0 = disable

1 = enable

TX FIFO

Interrupt

Flag

(read-only)

0 = not occurred

1 = occurred

TX FIFO

Interrupt

Flag

Clear

0 = no effect

1 = clear

C28x - Communications 11 - 9

Loading...

Loading...