Serial Communications Interface (SCI)

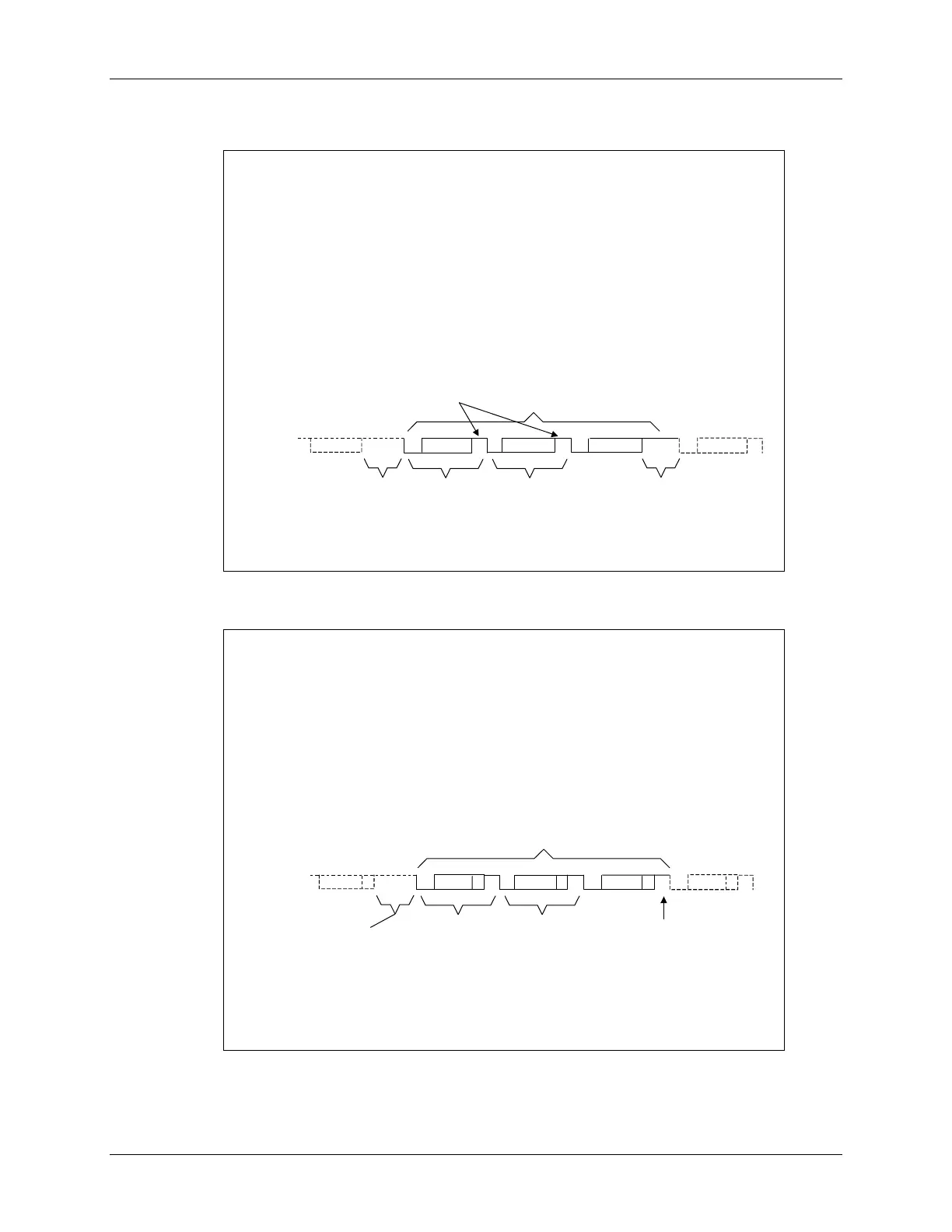

Idle-Line Wake-Up Mode

Idle time separates blocks of frames

Receiver wakes up when SCIRXD high for 10 or

more bit periods

Two transmit address methods

deliberate software delay of 10 or more bits

set TXWAKE bit to automatically leave exactly

11 idle bits

Last Data

ST

SPST Data

SCIRXD/

SCITXD

Block of Frames

SP SP

Last Data

ST Addr

SP

Idle

Period

10 bits

or greater

Idle

Period

10 bits

or greater

Address frame

follows 10 bit

or greater idle

1st data frame

SPST Addr

Idle periods

of less than

10 bits

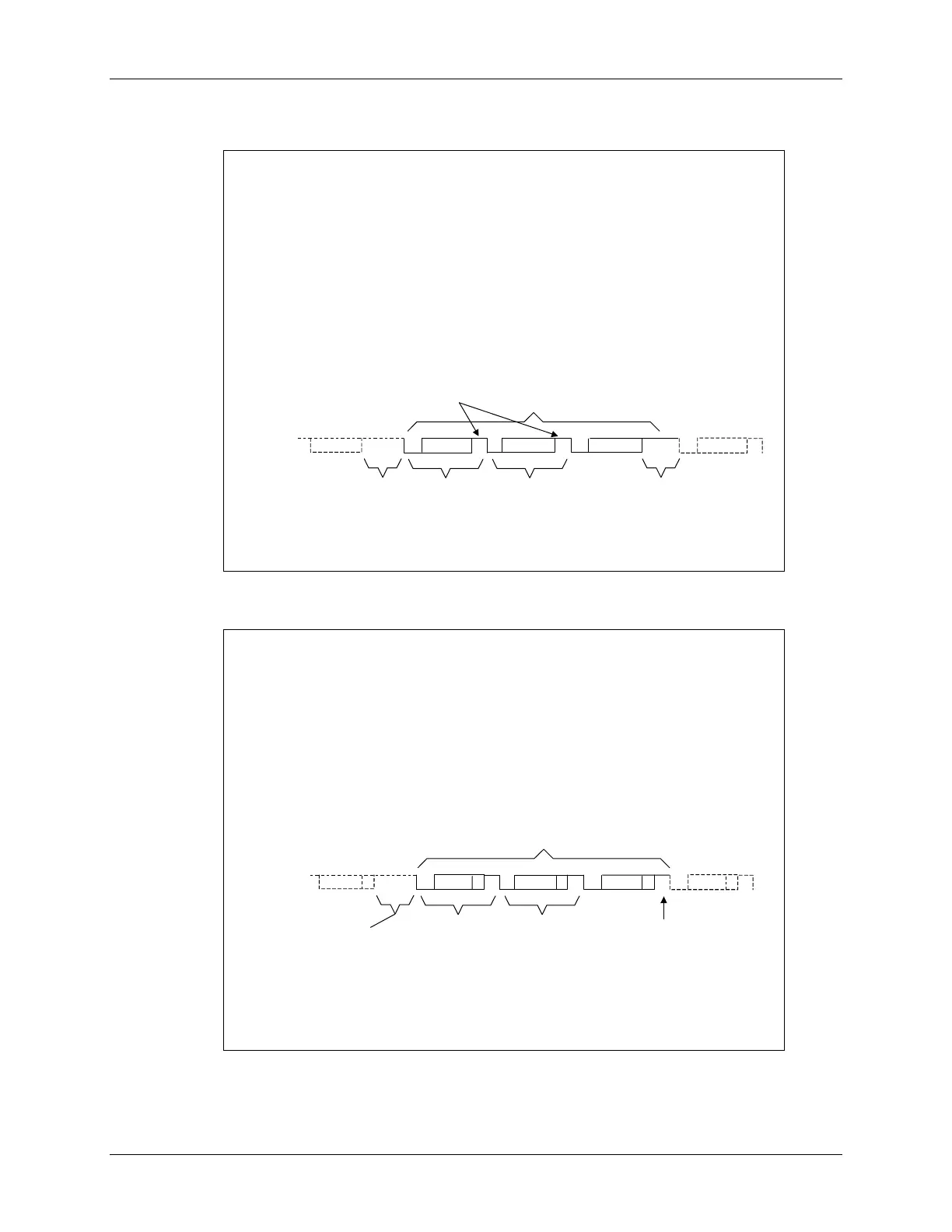

Address-Bit Wake-Up Mode

All frames contain an extra address bit

Receiver wakes up when address bit detected

Automatic setting of Addr/Data bit in frame by

setting TXWAKE = 1 prior to writing address to

SCITXBUF

Last Data

STST Data

SCIRXD/

SCITXD

Block of Frames

SP SP

Last Data

ST Addr

SP

Idle Period

length of no

significance

First frame within

block is Address.

ADDR/DATA

bit set to 1

1st data frame

0100

SPST Addr

1

SP

no additional

idle bits needed

beyond stop bits

C28x - Communications 11 - 15

Loading...

Loading...