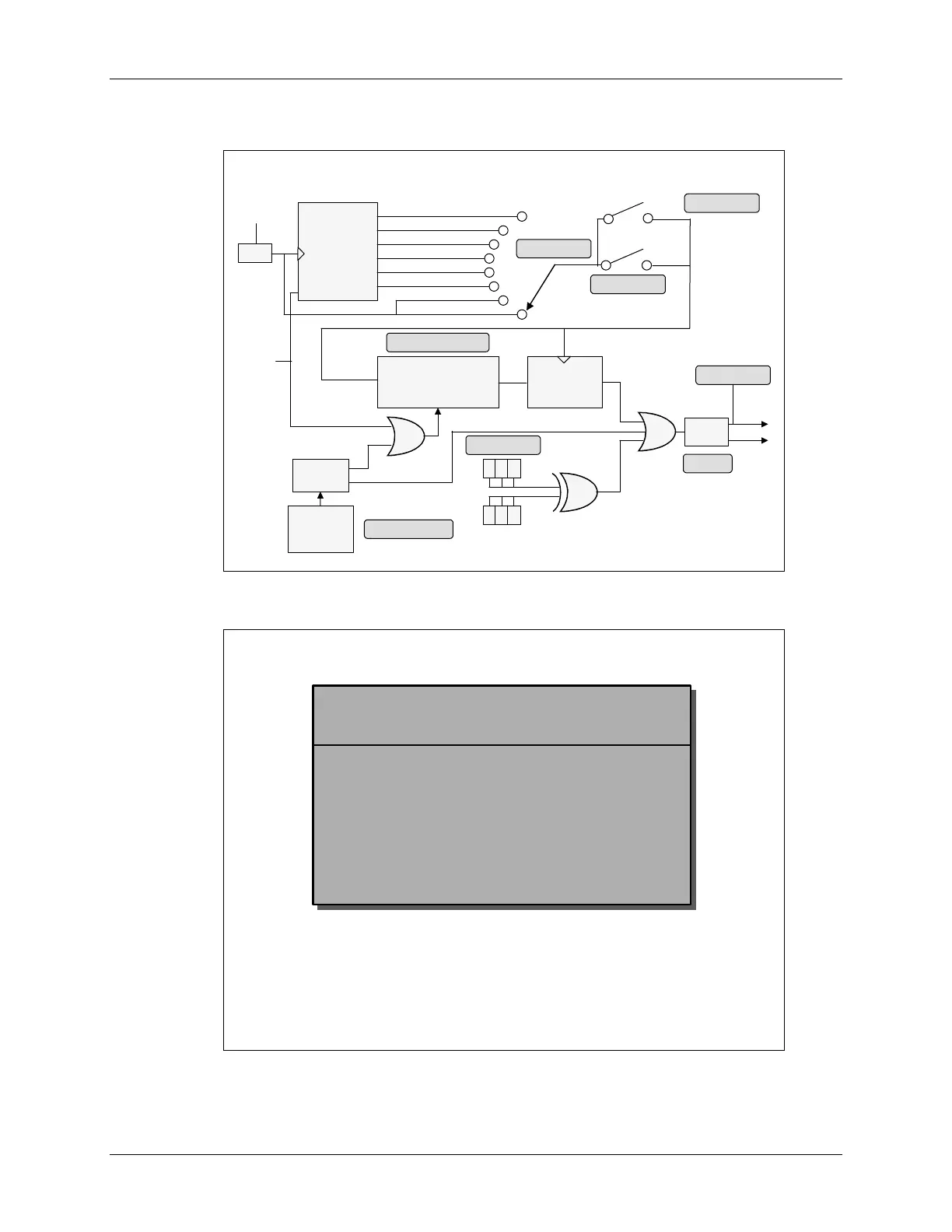

Watchdog Timer

Watchdog Timer Module

Watchdog Timer Module

(lab file:

(lab file:

SysCtrl

SysCtrl

.c)

.c)

6

6

-

-

Bit

Bit

Free

Free

-

-

Running

Running

Counter

Counter

CLR

CLR

/2

/2

/4

/4

/8

/8

/16

/16

/32

/32

/64

/64

OSCCLK

OSCCLK

System

System

Reset

Reset

101

101

100

100

011

011

010

010

001

001

000

000

111

111

110

110

•

•

•

•

•

•

•

•

8

8

-

-

Bit Watchdog

Bit Watchdog

Counter

Counter

CLR

CLR

One

One

-

-

Cycle

Cycle

Delay

Delay

Watchdog

Watchdog

Reset Key

Reset Key

Register

Register

55 + AA

55 + AA

Detector

Detector

•

•

Good Key

Good Key

Bad Key

Bad Key

1 0 1

1 0 1

•

•

•

•

•

•

•

•

/

/

/

/

3

3

3

3

WDCR . 2

WDCR . 2

-

-

0

0

WDCR . 6

WDCR . 6

WDPS

WDPS

WDDIS

WDDIS

WDCR . 7

WDCR . 7

WDFLAG

WDFLAG

WDCNTR . 7

WDCNTR . 7

-

-

0

0

WDKEY . 7

WDKEY . 7

-

-

0

0

WDCR . 5

WDCR . 5

-

-

3

3

WDCHK 2

WDCHK 2

-

-

0

0

Bad WDCR Key

Bad WDCR Key

/512

/512

Output

Output

Pulse

Pulse

WDRST

WDRST

WDINT

WDINT

SCSR .1

SCSR .1

WDENINT

WDENINT

•

•

•

•

•

•

SCSR . 0

SCSR . 0

WDOVERRIDE

WDOVERRIDE

WDPS FRC C28x timeout

Bits rollover period @ 150 MHz

00x: 1 4.37 ms

010: 2 8.74 ms

011: 4 17.48 ms

100: 8 34.96 ms

101: 16 69.92 ms

110: 32 139.84 ms

111: 64 279.68 ms

WDPS

WDPS

FRC

FRC

C28x timeout

C28x timeout

Bits

Bits

rollover

rollover

period @ 150 MHz

period @ 150 MHz

00x:

00x:

1 4.37 ms

1 4.37 ms

010: 2 8.74 ms

010: 2 8.74 ms

011: 4 17.48 ms

011: 4 17.48 ms

100: 8 34.96 ms

100: 8 34.96 ms

101: 16 69.92 ms

101: 16 69.92 ms

110: 32 139.84 ms

110: 32 139.84 ms

111: 64 279.68 ms

111: 64 279.68 ms

Watchdog Period Selection

Watchdog Period Selection

WDPS set to 000 after any CPU reset

WDPS set to 000 after any CPU reset

Watchdog starts counting immediately after reset

Watchdog starts counting immediately after reset

is released

is released

(for OSCCLK = 30 MHz

(for OSCCLK = 30 MHz

⇒

⇒

(1/30 MHz) * (512*256) = 4.37 ms)

(1/30 MHz) * (512*256) = 4.37 ms)

5 - 6 C28x - System Initialization

Loading...

Loading...