RM46L852

SPNS185 –SEPTEMBER 2012

www.ti.com

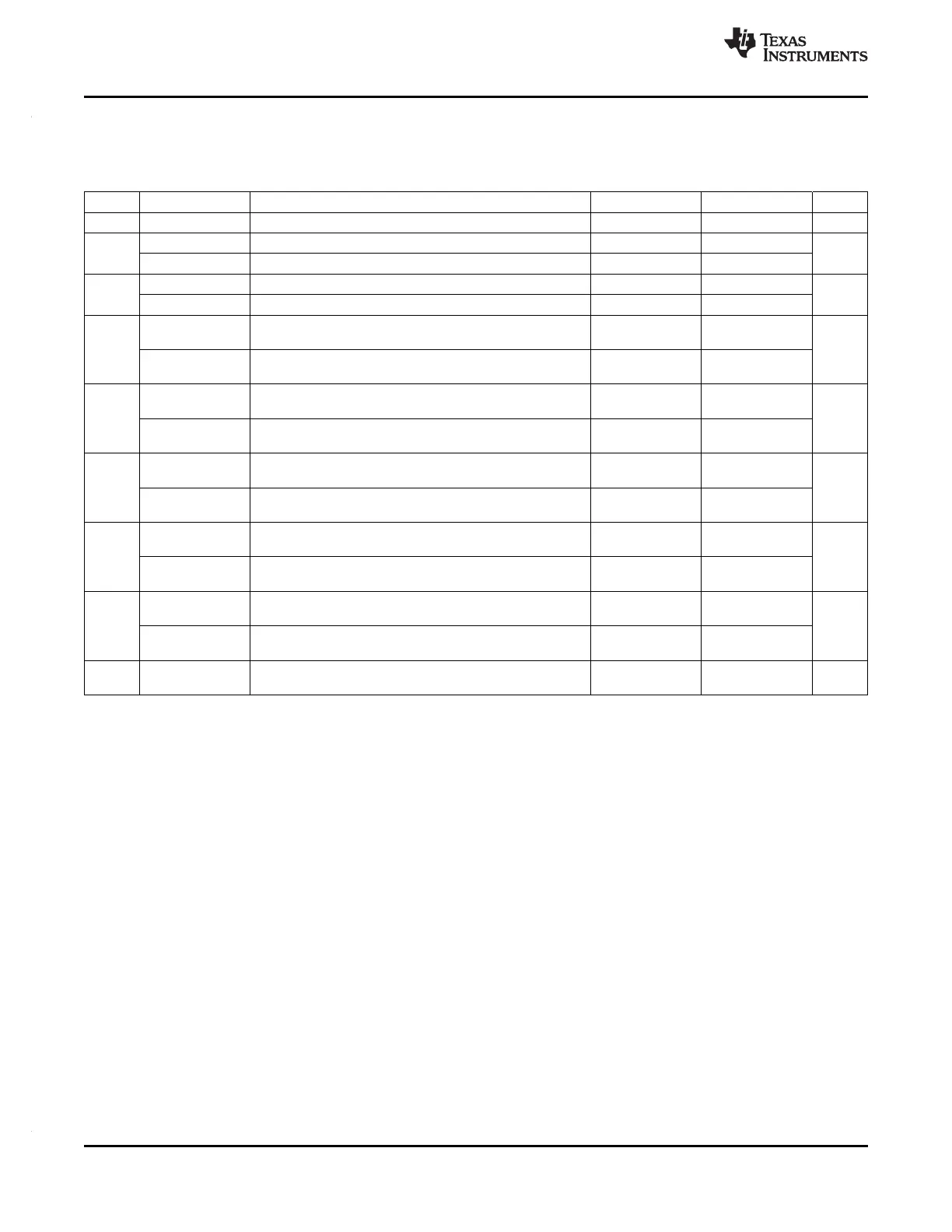

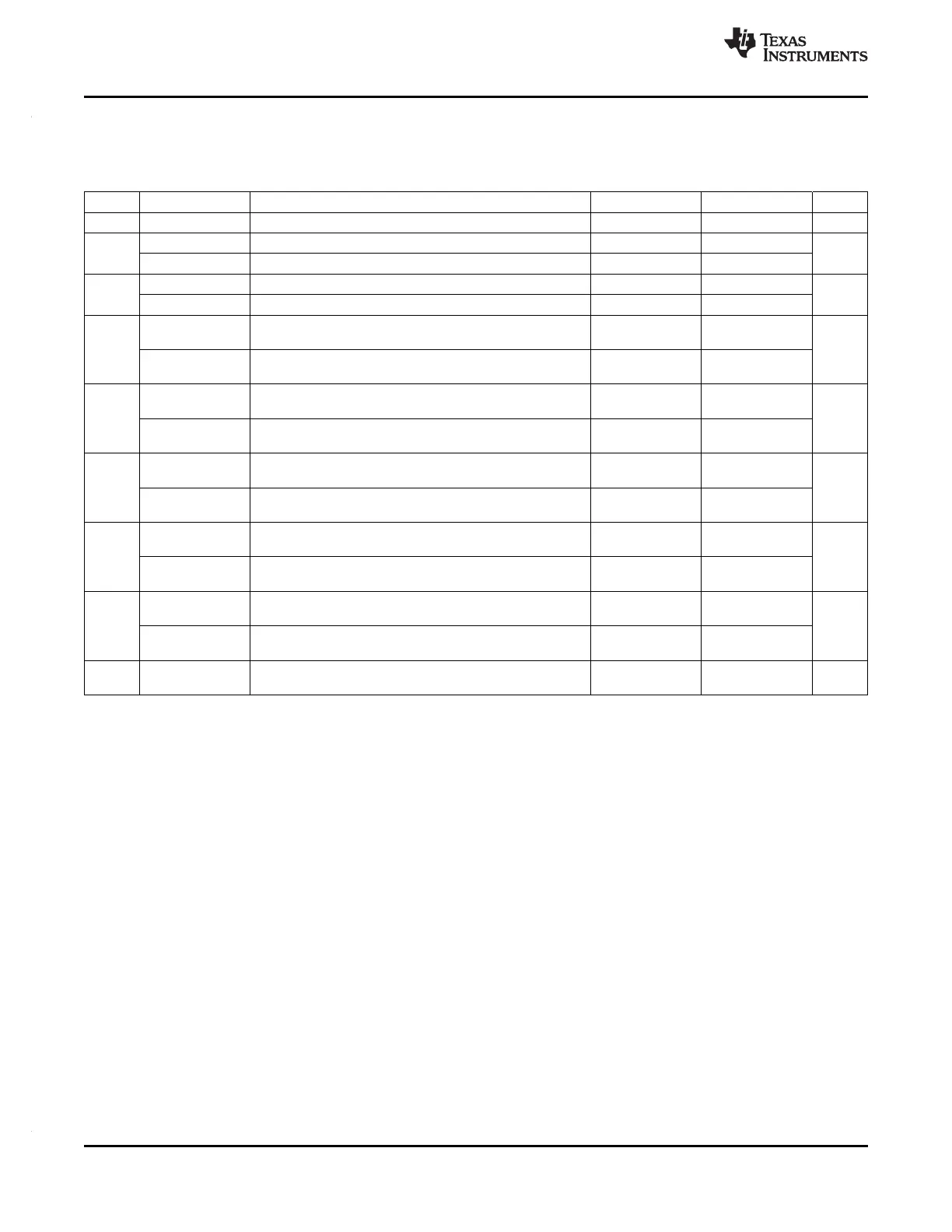

5.11.5 SPI Slave Mode I/O Timings

Table 5-34. SPI Slave Mode External Timing Parameters (CLOCK PHASE = 0, SPICLK = input, SPISIMO =

input, and SPISOMI = output)

(1)(2)(3)(4)

NO. Parameter MIN MAX Unit

1 t

c(SPC)S

Cycle time, SPICLK

(5)

40 256t

c(VCLK)

ns

2

(6)

t

w(SPCH)S

Pulse duration, SPICLK high (clock polarity = 0) 14 ns

t

w(SPCL)S

Pulse duration, SPICLK low (clock polarity = 1) 14

3

(6)

t

w(SPCL)S

Pulse duration, SPICLK low (clock polarity = 0) 14 ns

t

w(SPCH)S

Pulse duration, SPICLK high (clock polarity = 1) 14

4

(6)

t

d(SPCH-SOMI)S

Delay time, SPISOMI valid after SPICLK high (clock t

rf(SOMI)

+ 13 ns

polarity = 0)

t

d(SPCL-SOMI)S

Delay time, SPISOMI valid after SPICLK low (clock polarity t

rf(SOMI)

+ 13

= 1)

5

(6)

t

h(SPCH-SOMI)S

Hold time, SPISOMI data valid after SPICLK high (clock 2 ns

polarity =0)

t

h(SPCL-SOMI)S

Hold time, SPISOMI data valid after SPICLK low (clock 2

polarity =1)

6

(6)

t

su(SIMO-SPCL)S

Setup time, SPISIMO before SPICLK low (clock polarity = 2 ns

0)

t

su(SIMO-SPCH)S

Setup time, SPISIMO before SPICLK high (clock polarity = 2

1)

7

(6)

t

h(SPCL-SIMO)S

Hold time, SPISIMO data valid after SPICLK low (clock 2 ns

polarity = 0)

t

h(SPCH-SIMO)S

Hold time, SPISIMO data valid after S PICLK high (clock 2

polarity = 1)

8 t

d(SPCL-SENAH)S

Delay time, SPIENAn high after last SPICLK low (clock 1.5t

c(VCLK)

2.5t

c(VCLK)

+t

r(ENAn)

ns

polarity = 0)

t

d(SPCH-SENAH)S

Delay time, SPIENAn high after last SPICLK high (clock 1.5t

c(VCLK)

2.5t

c(VCLK)

+

tr(ENAn)

polarity = 1)

9 t

d(SCSL-SENAL)S

Delay time, SPIENAn low after SPICSn low (if new data t

f(ENAn)

t

c(VCLK)

+t

f(ENAn)

+1 ns

has been written to the SPI buffer) 4

(1) The MASTER bit (SPIGCR1.0) is set and the CLOCK PHASE bit (SPIFMTx.16) is set.

(2) If the SPI is in slave mode, the following must be true: t

c(SPC)S

≥ (PS + 1) t

c(VCLK)

, where PS = prescale value set in SPIFMTx.[15:8].

(3) For rise and fall timings, see Table 3-4.

(4) t

c(VCLK)

= interface clock cycle time = 1 /f

(VCLK)

(5) When the SPI is in Slave mode, the following must be true:

For PS values from 1 to 255: t

c(SPC)S

≥ (PS +1)t

c(VCLK)

≥ 40ns, where PS is the prescale value set in the SPIFMTx.[15:8] register bits.

For PS values of 0: t

c(SPC)S

= 2t

c(VCLK)

≥ 40ns.

(6) The active edge of the SPICLK signal referenced is controlled by the CLOCK POLARITY bit (SPIFMTx.17).

156 Peripheral Information and Electrical Specifications Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Loading...

Loading...