1

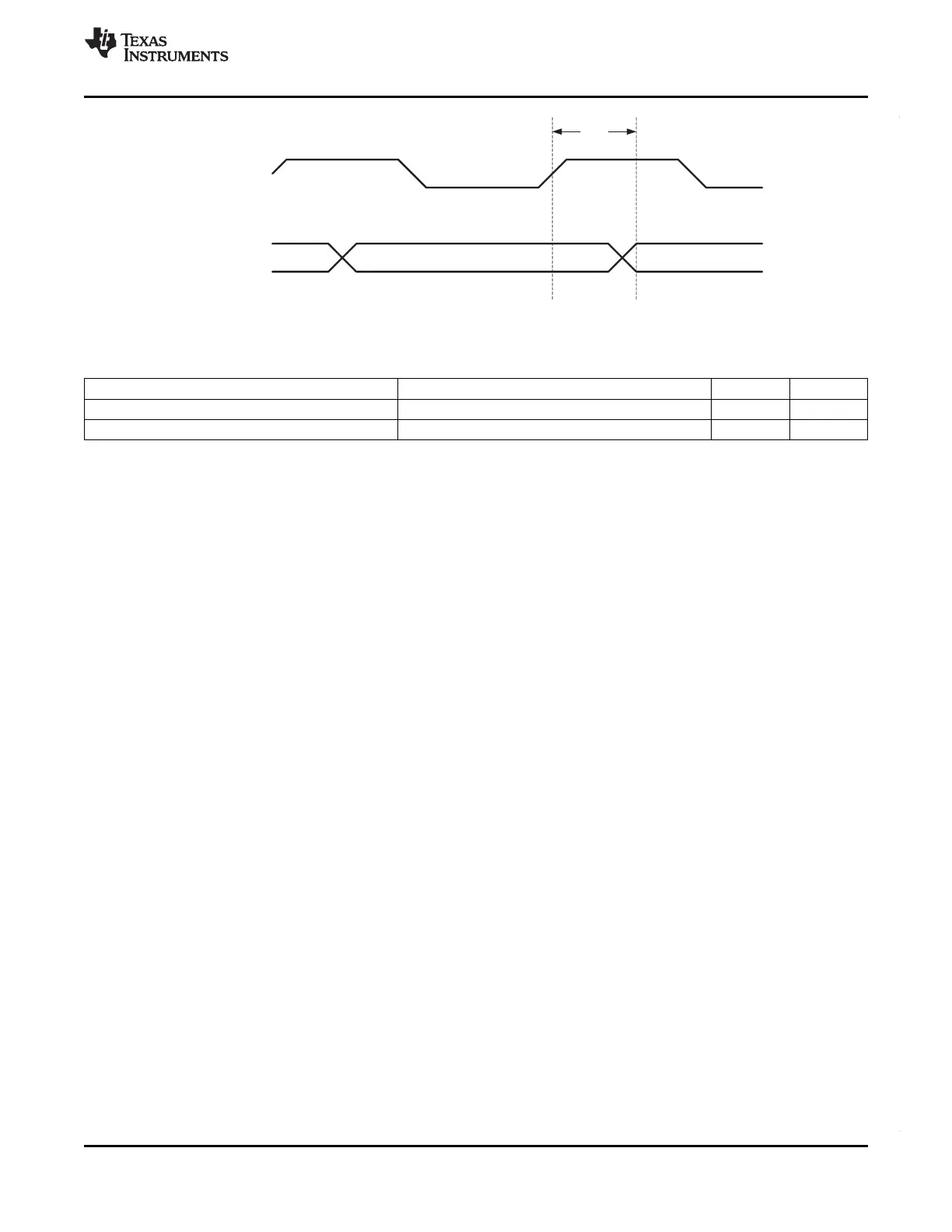

MII_MTCLK

MII_MTXD

MII_MTXEN

VALID

RM46L852

www.ti.com

SPNS185 –SEPTEMBER 2012

Figure 5-23. MII Transmit Timing

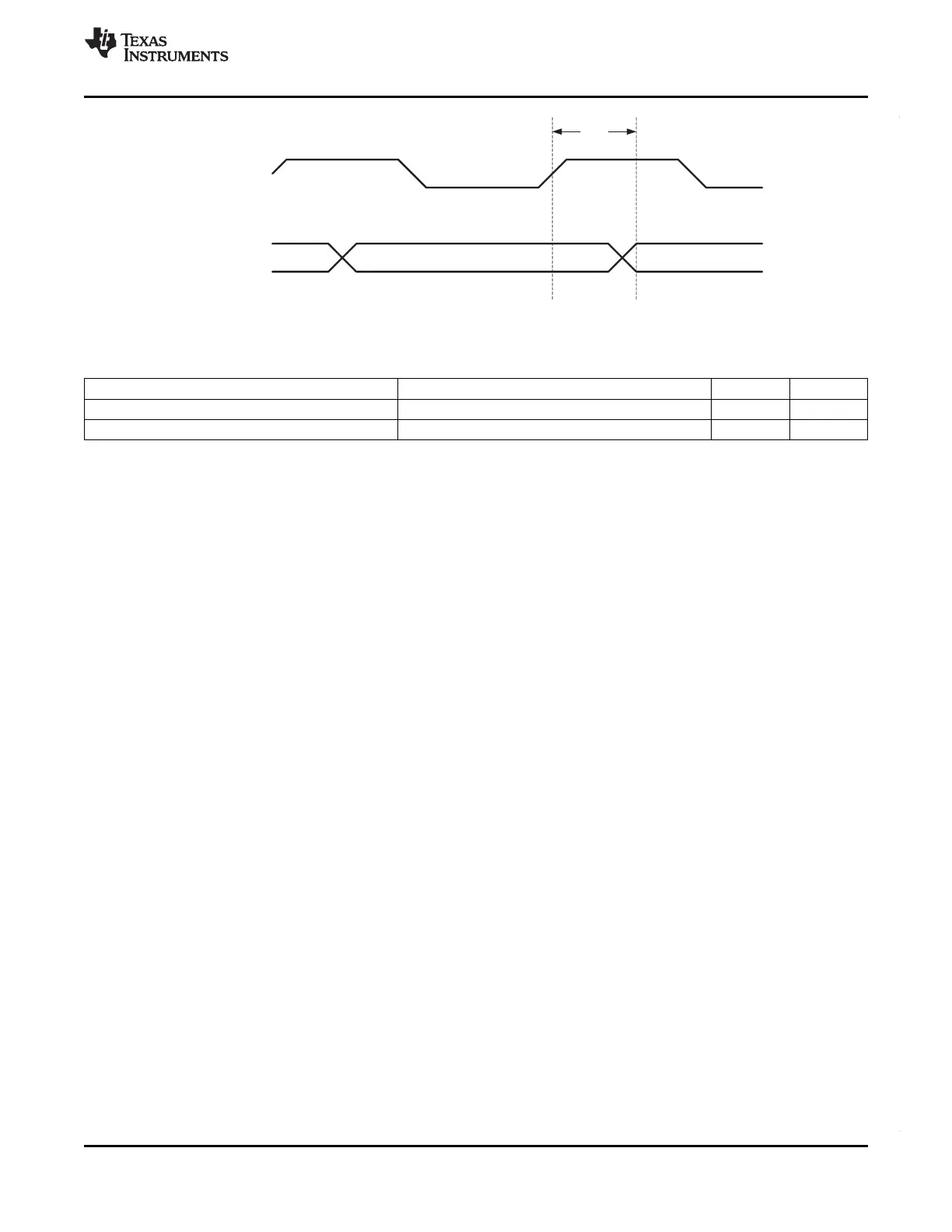

Table 5-37. MII Transmit Timing

Parameter Description MIN MAX

t

d(MIIMTXD)

Delay time, MIIMTCLK rising edge to MIIMTXD 5ns 25ns

t

d(MIIMTXEN)

Delay time, MIIMTCLK rising edge to MIIMTXEN 5ns 25ns

Copyright © 2012, Texas Instruments Incorporated Peripheral Information and Electrical Specifications 161

Submit Documentation Feedback

Loading...

Loading...