RM46L852

www.ti.com

SPNS185 –SEPTEMBER 2012

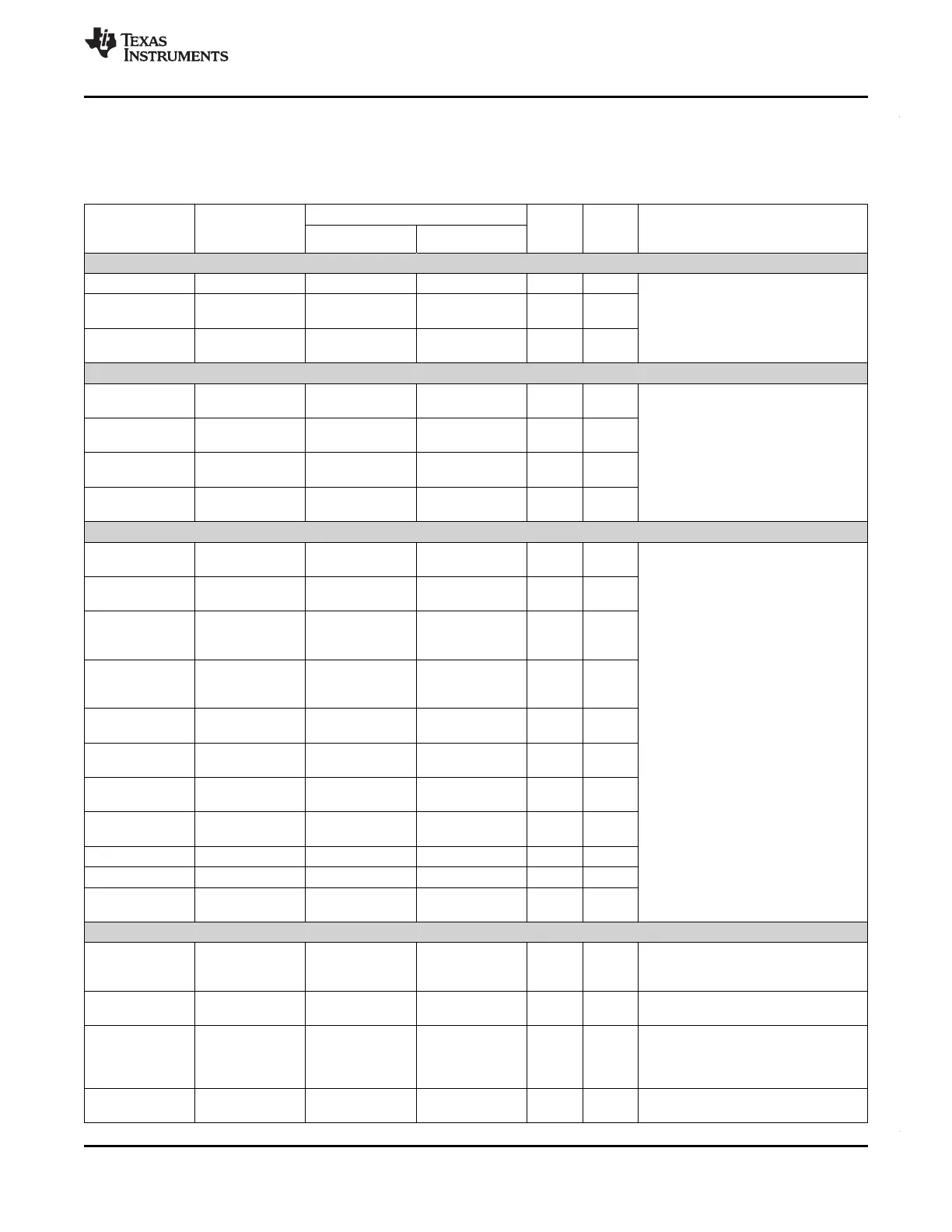

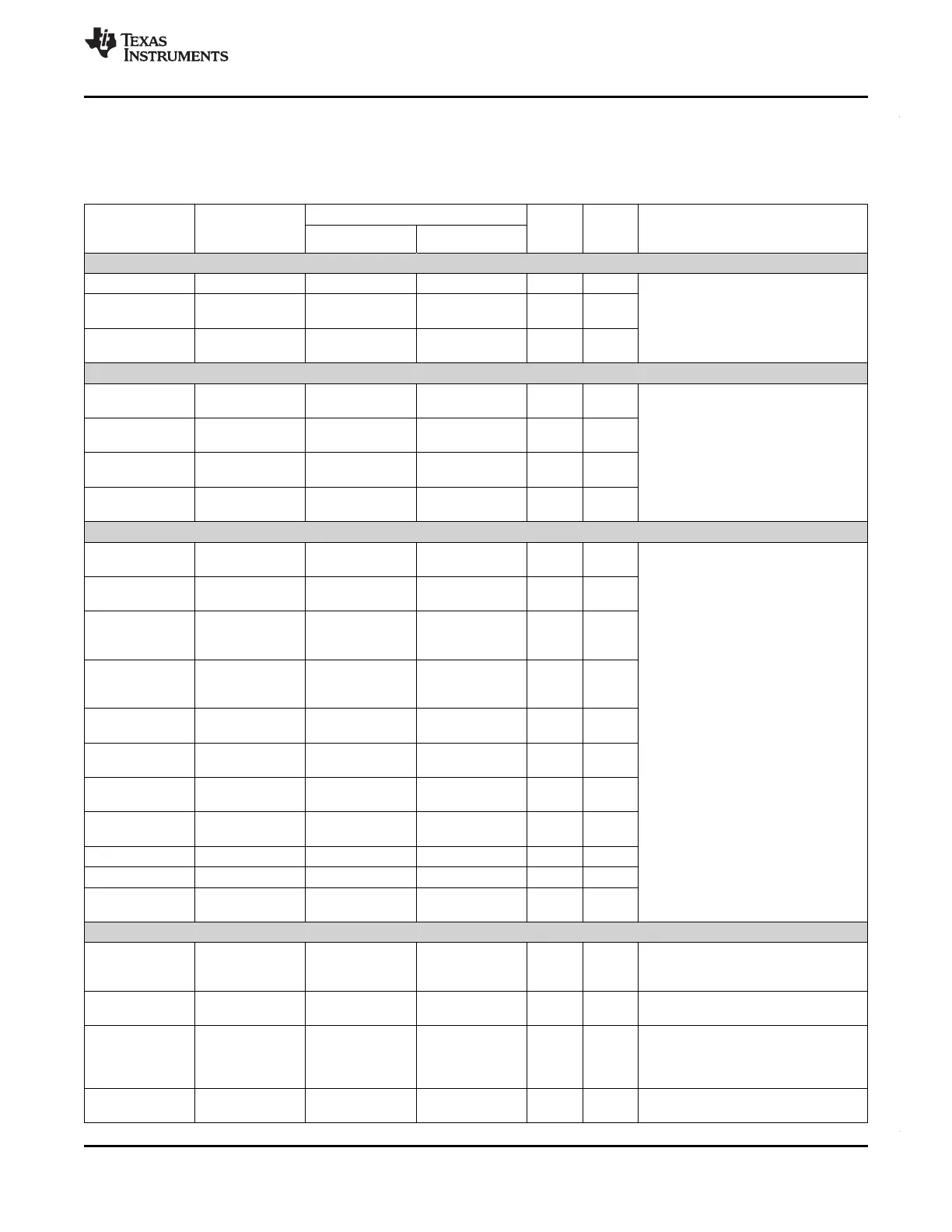

4.9.2 Memory Map Table

Please refer to for a block diagrams showing the devices interconnect.

Table 4-21. Device Memory Map

FRAME ADDRESS RANGE RESPNSE FOR ACCESS TO

FRAME CHIP FRAME ACTUA

MODULE NAME UNIMPLEMENTED LOCATIONS IN

SELECT SIZE L SIZE

START END

FRAME

Memories tightly coupled to the ARM Cortex-R4F CPU

TCM Flash CS0 0x0000_0000 0x00FF_FFFF 16MB 1.25MB

TCM RAM + RAM

CSRAM0 0x0800_0000 0x0BFF_FFFF 64MB 192kB

ECC Abort

Flash mirror

Mirrored Flash 0x2000_0000 0x20FF_FFFF 16MB 1.25MB

frame

External Memory Accesses

EMIF Chip Select

EMIF select 2 0x6000_0000 0x63FF_FFFF 64MB 32kB

2 (asynchronous)

EMIF Chip Select

EMIF select 3 0x6400_0000 0x67FF_FFFF 64MB 32kB

3 (asynchronous)

Access to "Reserved" space will

generate Abort

EMIF Chip Select

EMIF select 4 0x6800_0000 0x6BFF_FFFF 64MB 32kB

4 (asynchronous)

EMIF Chip Select

EMIF select 0 0x8000_0000 0x87FF_FFFF 128MB 64MB

0 (synchronous)

Flash Module Bus2 Interface

Customer OTP,

0xF000_0000 0xF000_1FFF 8kB 4kB

TCM Flash Banks

Customer OTP,

0xF000_E000 0xF000_FFFF 8kB 4kB

Bank 7

Customer

OTP–ECC, TCM 0xF004_0000 0xF004_03FF 1kB 512B

Flash Banks

Customer

OTP–ECC, 0xF004_1C00 0xF004_1FFF 1kB 512B

Bank 7

TI OTP, TCM

0xF008_0000 0xF008_1FFF 8kB 4kB

Abort

Flash Banks

TI OTP,

0xF008_E000 0xF008_FFFF 8kB 4kB

Bank 7

TI OTP–ECC,

0xF00C_0000 0xF00C_03FF 1kB 512B

TCM Flash Banks

TI OTP–ECC,

0xF00C_1C00 0xF00C_1FFF 1kB 512B

Bank 7

Bank 7 – ECC 0xF010_0000 0xF013_FFFF 256kB 8kB

Bank 7 0xF020_0000 0xF03F_FFFF 2MB 64kB

Flash Data Space

0xF040_0000 0xF04F_FFFF 1MB 160kB

ECC

Ethernet and EMIF slave interfaces

CPPI Memory

Slave (Ethernet 0xFC52_0000 0xFC52_1FFF 8kB 8kB Abort

RAM)

CPGMAC Slave

0xFCF7_8000 0xFCF7_87FF 2kB 2kB No error

(Ethernet Slave)

CPGMACSS

Wrapper

0xFCF7_8800 0xFCF7_88FF 256B 256B No error

(Ethernet

Wrapper)

Ethernet MDIO

0xFCF7_8900 0xFCF7_89FF 256B 256B No error

Interface

Copyright © 2012, Texas Instruments Incorporated System Information and Electrical Specifications 75

Submit Documentation Feedback

Loading...

Loading...