196

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical Specifications Copyright © 2009–2017, Texas Instruments Incorporated

6.22 Ethernet Media Access Controller (EMAC)

The Ethernet Media Access Controller (EMAC) provides an efficient interface between device and the

network. The EMAC supports both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps

in either half- or full-duplex mode, with hardware flow control and quality of service (QOS) support.

The EMAC controls the flow of packet data from the device to the PHY. The MDIO module controls PHY

configuration and status monitoring.

Both the EMAC and the MDIO modules interface to the device through a custom interface that allows

efficient data transmission and reception. This custom interface is referred to as the EMAC control

module, and is considered integral to the EMAC/MDIO peripheral. The control module is also used to

multiplex and control interrupts.

6.22.1 EMAC Peripheral Register Description(s)

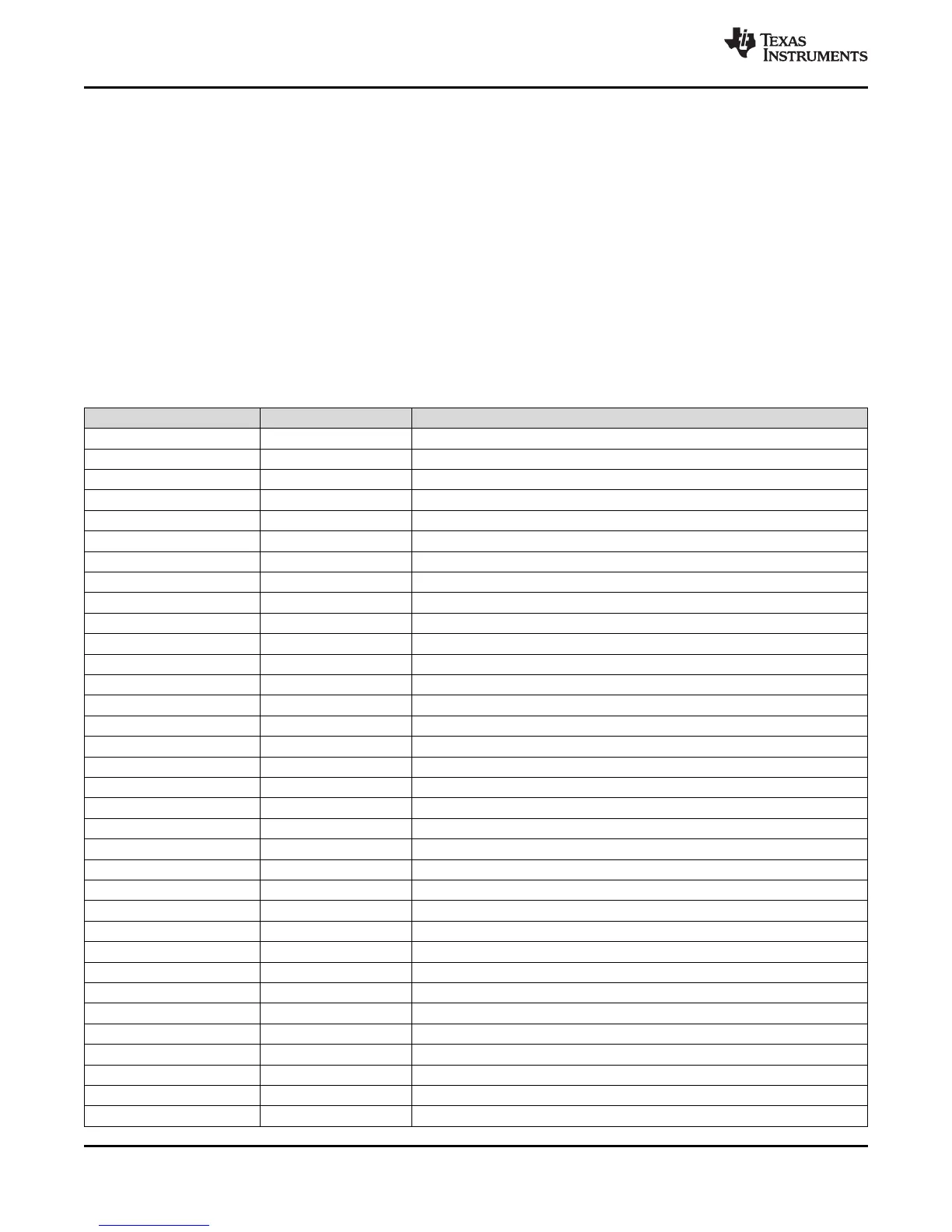

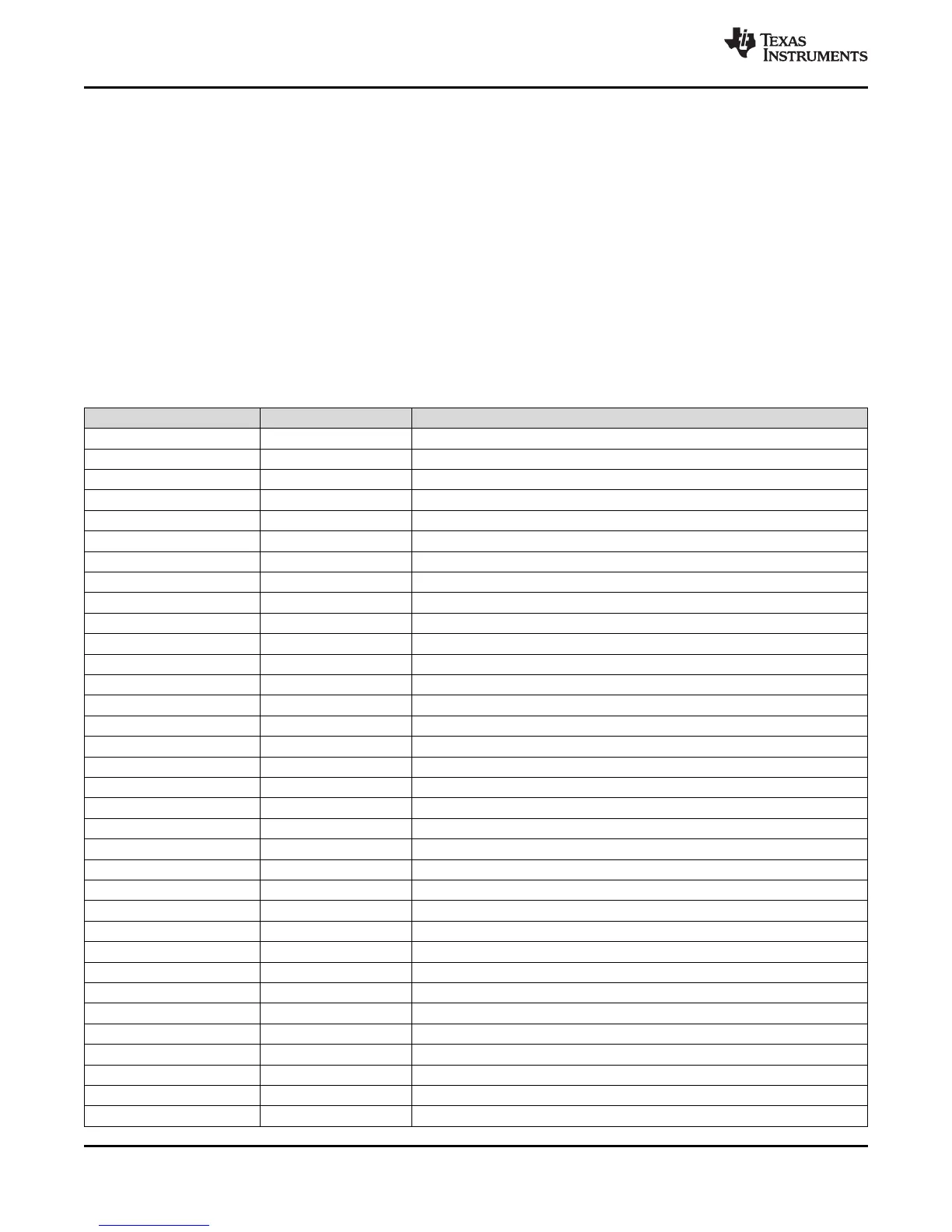

Table 6-94. Ethernet Media Access Controller (EMAC) Registers

BYTE ADDRESS ACRONYM REGISTER DESCRIPTION

0x01E2 3000 TXREV Transmit Revision Register

0x01E2 3004 TXCONTROL Transmit Control Register

0x01E2 3008 TXTEARDOWN Transmit Teardown Register

0x01E2 3010 RXREV Receive Revision Register

0x01E2 3014 RXCONTROL Receive Control Register

0x01E2 3018 RXTEARDOWN Receive Teardown Register

0x01E2 3080 TXINTSTATRAW Transmit Interrupt Status (Unmasked) Register

0x01E2 3084 TXINTSTATMASKED Transmit Interrupt Status (Masked) Register

0x01E2 3088 TXINTMASKSET Transmit Interrupt Mask Set Register

0x01E2 308C TXINTMASKCLEAR Transmit Interrupt Clear Register

0x01E2 3090 MACINVECTOR MAC Input Vector Register

0x01E2 3094 MACEOIVECTOR MAC End Of Interrupt Vector Register

0x01E2 30A0 RXINTSTATRAW Receive Interrupt Status (Unmasked) Register

0x01E2 30A4 RXINTSTATMASKED Receive Interrupt Status (Masked) Register

0x01E2 30A8 RXINTMASKSET Receive Interrupt Mask Set Register

0x01E2 30AC RXINTMASKCLEAR Receive Interrupt Mask Clear Register

0x01E2 30B0 MACINTSTATRAW MAC Interrupt Status (Unmasked) Register

0x01E2 30B4 MACINTSTATMASKED MAC Interrupt Status (Masked) Register

0x01E2 30B8 MACINTMASKSET MAC Interrupt Mask Set Register

0x01E2 30BC MACINTMASKCLEAR MAC Interrupt Mask Clear Register

0x01E2 3100 RXMBPENABLE Receive Multicast/Broadcast/Promiscuous Channel Enable Register

0x01E2 3104 RXUNICASTSET Receive Unicast Enable Set Register

0x01E2 3108 RXUNICASTCLEAR Receive Unicast Clear Register

0x01E2 310C RXMAXLEN Receive Maximum Length Register

0x01E2 3110 RXBUFFEROFFSET Receive Buffer Offset Register

0x01E2 3114 RXFILTERLOWTHRESH Receive Filter Low Priority Frame Threshold Register

0x01E2 3120 RX0FLOWTHRESH Receive Channel 0 Flow Control Threshold Register

0x01E2 3124 RX1FLOWTHRESH Receive Channel 1 Flow Control Threshold Register

0x01E2 3128 RX2FLOWTHRESH Receive Channel 2 Flow Control Threshold Register

0x01E2 312C RX3FLOWTHRESH Receive Channel 3 Flow Control Threshold Register

0x01E2 3130 RX4FLOWTHRESH Receive Channel 4 Flow Control Threshold Register

0x01E2 3134 RX5FLOWTHRESH Receive Channel 5 Flow Control Threshold Register

0x01E2 3138 RX6FLOWTHRESH Receive Channel 6 Flow Control Threshold Register

0x01E2 313C RX7FLOWTHRESH Receive Channel 7 Flow Control Threshold Register

Loading...

Loading...