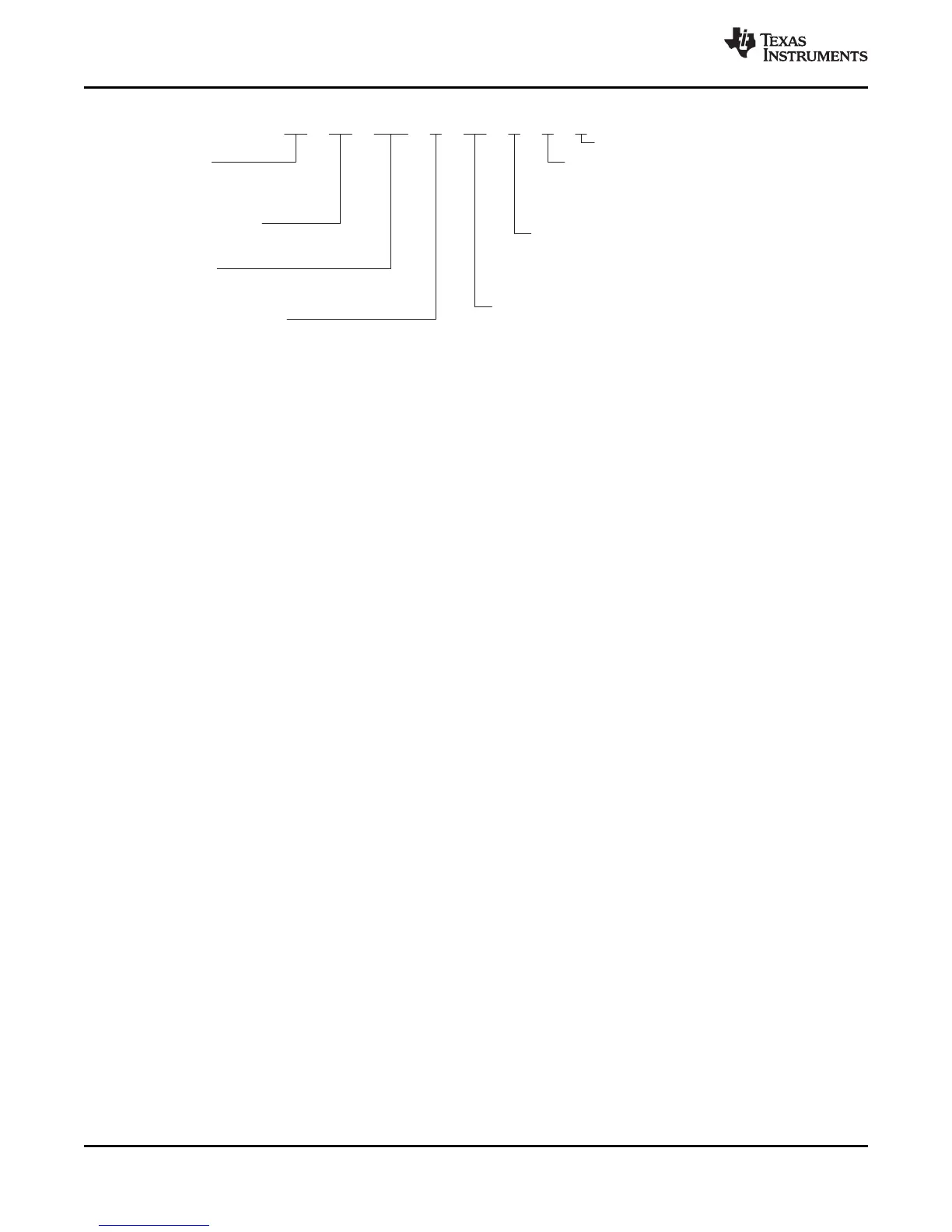

TMS

320

C6748

( )

ZWT

( ) ( )

PREFIX

TMX = Experimental Device

TMS = Qualified Device

DEVICE FAMILY

320 = TMS320™ DSP Family

DEVICE

C6748

DEVICE SPEED RANGE

3 = 300 MHz (Revision 1.x)

TEMPERATURE RANGE (JUNCTION)

Blank = 0°C to 90°C, Commercial Grade

PACKAGE TYPE

(A)

361-Pin Plastic BGA, with Pb-free Soldered

Balls [Green], 0.65-mm Ball Pitch

ZCE =

SILICON REVISION

Blank = Revision 1.0

ZWT = 361-Pin Plastic BGA, with Pb-free Soldered

Balls [Green], 0.8-mm Ball Pitch

A = Revision 1.1

B = Revision 2.0

E = Revision 2.3

4 = 456 MHz (Revision 2.x)

3 = 375 MHz (Revision 2.x)

A = –40°C to 105°C, Extended Grade

D = –40°C to 90°C, Industrial Grade

(B)

E

Basic Secure Boot Enabled

264

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device and Documentation Support Copyright © 2009–2017, Texas Instruments Incorporated

A. BGA = Ball Grid Array

B. Parts marked revision B are silicon revision 2.1 if '21' is marked on the package, and silicon revision 2.0 if there is no

'21' marking.

Figure 7-1. Device Nomenclature

7.2 Tools and Software

Software

Code Composer Studio™ Integrated Development Environment (IDE): including Editor

C/C++/Assembly Code Generation, and Debug plus additional development tools

Scalable, Real-Time Foundation Software (DSP/BIOS™) provides the basic run-time target software

needed to support any application.

Development Tools

Extended Development System (XDS ™) Emulator For a complete listing of development-support tools

for the device, visit the Texas Instruments web site on the Worldwide Web at

http://www.ti.com uniform resource locator (URL). For information on pricing and availability,

contact the nearest TI field sales office or authorized distributor.

7.3 Documentation Support

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the

upper right corner, click on Alert me to register and receive a weekly digest of any product information that

has changed. For change details, review the revision history included in any revised document.

The current documentation that describes the DSP, related peripherals, and other technical collateral is

listed below.

User's Guides

SPRUG82 TMS320C674x DSP Cache User's Guide. Explains the fundamentals of memory caches

and describes how the two-level cache-based internal memory architecture in the

TMS320C674x digital signal processor (DSP) can be efficiently used in DSP applications.

Shows how to maintain coherence with external memory, how to use DMA to reduce

memory latencies, and how to optimize your code to improve cache efficiency. The internal

memory architecture in the C674x DSP is organized in a two-level hierarchy consisting of a

dedicated program cache (L1P) and a dedicated data cache (L1D) on the first level.

Accesses by the CPU to the these first level caches can complete without CPU pipeline

stalls. If the data requested by the CPU is not contained in cache, it is fetched from the next

lower memory level, L2 or external memory.

SPRUFE8 TMS320C674x DSP CPU and Instruction Set Reference Guide. Describes the CPU

architecture, pipeline, instruction set, and interrupts for the TMS320C674x digital signal

processors (DSPs). The C674x DSP is an enhancement of the C64x+ and C67x+ DSPs with

added functionality and an expanded instruction set.

Loading...

Loading...